**Budapest University of Technology and Economics** Faculty of Electrical Engineering and Informatics Department of Measurement and Information Systems

# Handling Axiomatic Memory Models in Abstraction-Based Model Checking of Concurrent and Distributed Systems

MASTER'S THESIS

Author Levente Bajczi Advisor Dr. Vince Molnár

### HALLGATÓI NYILATKOZAT

Alulírott *Bajczi Levente*, szigorló hallgató kijelentem, hogy ezt a diplomatervet meg nem engedett segítség nélkül, saját magam készítettem, csak a megadott forrásokat (szakirodalom, eszközök stb.) használtam fel. Minden olyan részt, melyet szó szerint, vagy azonos értelemben, de átfogalmazva más forrásból átvettem, egyértelműen, a forrás megadásával megjelöltem.

Hozzájárulok, hogy a jelen munkám alapadatait (szerző(k), cím, angol és magyar nyelvű tartalmi kivonat, készítés éve, konzulens(ek) neve) a BME VIK nyilvánosan hozzáférhető elektronikus formában, a munka teljes szövegét pedig az egyetem belső hálózatán keresztül (vagy autentikált felhasználók számára) közzétegye. Kijelentem, hogy a benyújtott munka és annak elektronikus verziója megegyezik. Dékáni engedéllyel titkosított diplomatervek esetén a dolgozat szövege csak 3 év eltelte után válik hozzáférhetővé.

Budapest, 2022. május 29.

Bajczi Levente hallgató

# Contents

| K        | ivona | at       |                                                      | i  |

|----------|-------|----------|------------------------------------------------------|----|

| A        | bstra | ct       |                                                      | ii |

| 1        | Intr  | oducti   | on                                                   | 1  |

| <b>2</b> | nd    | 3        |                                                      |    |

|          | 2.1   | Safety   | -Critical Systems                                    | 3  |

|          | 2.2   | Forma    | l Software Verification                              | 4  |

|          |       | 2.2.1    | Bounded Model Checking (BMC)                         | 7  |

|          |       | 2.2.2    | Counterexample-Guided Abstraction Refinement (CEGAR) | 8  |

|          |       |          | 2.2.2.1 A Generic CEGAR Loop                         | 8  |

|          |       |          | 2.2.2.2 CEGAR Configuration Options                  | 9  |

|          |       |          | 2.2.2.3 BMC Inside CEGAR                             | 13 |

|          | 2.3   | Multi-   | Processor Architectures                              | 13 |

|          |       | 2.3.1    | Memory Consistency Models                            | 13 |

|          |       |          | 2.3.1.1 Event Sets, Relations and Constraints        | 14 |

|          | 2.4   | Analy    | sis of Multi-Threaded Programs                       | 16 |

|          |       | 2.4.1    | Interleaving Semantics                               | 16 |

|          |       | 2.4.2    | Declarative Semantics                                | 18 |

|          |       | 2.4.3    | Multi-Threaded CFA                                   | 18 |

| 3        | Stat  | te of tl | ne Art                                               | 20 |

|          | 3.1   | Seque    | ntially Ordered Concurrency                          | 20 |

|          | 3.2   | Weakl    | y Ordered Concurrency                                | 20 |

|          |       | 3.2.1    | Herd                                                 | 21 |

|          |       | 3.2.2    | RCMC                                                 | 22 |

|          |       |          | 3.2.2.1 GenMC                                        | 23 |

|          |       | 3.2.3    | DARTAGNAN                                            | 24 |

| 4        | $\mathbf{SM}$              | IT-Based Verification over Declarative Semantics   25              |    |  |  |  |  |

|----------|----------------------------|--------------------------------------------------------------------|----|--|--|--|--|

|          | 4.1                        | Representing the Input Program                                     | 25 |  |  |  |  |

|          |                            | 4.1.1 Parsing C Programs                                           | 27 |  |  |  |  |

|          | 4.1.2 Parsing Litmus Tests |                                                                    |    |  |  |  |  |

|          | 4.2                        | Representing the Memory Model                                      | 28 |  |  |  |  |

|          | 4.3                        | Implementing the Core Algorithm                                    | 29 |  |  |  |  |

|          |                            | 4.3.1 Overview of the Approach                                     | 29 |  |  |  |  |

|          |                            | 4.3.2 Encoding Control and Data Flow                               | 29 |  |  |  |  |

|          |                            | 4.3.3 Encoding the Memory Model                                    | 31 |  |  |  |  |

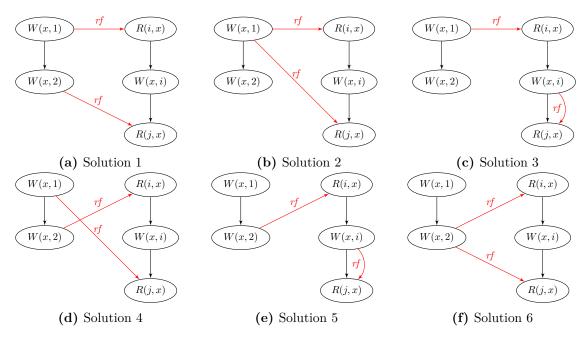

|          |                            | 4.3.4 Enumerating Solutions                                        | 32 |  |  |  |  |

|          | 4.4                        | Encoding Well-Formedness Constraints                               | 32 |  |  |  |  |

|          | 4.5                        | Providing a User Interface                                         | 34 |  |  |  |  |

|          | 4.6                        | Verifying the Implementation                                       | 35 |  |  |  |  |

| <b>5</b> | Abs                        | straction-Based State Space Exploration over Declarative Semantics | 36 |  |  |  |  |

|          | 5.1                        | High-Level Overview                                                | 36 |  |  |  |  |

|          | 5.2                        | Representative Example                                             | 37 |  |  |  |  |

|          | 5.3                        | Formalization                                                      | 39 |  |  |  |  |

|          |                            | 5.3.1 Data Structures                                              | 40 |  |  |  |  |

|          |                            | 5.3.2 Algorithms                                                   | 40 |  |  |  |  |

|          |                            | 5.3.2.1 Overview                                                   | 40 |  |  |  |  |

|          |                            | 5.3.2.2 Abstract                                                   | 41 |  |  |  |  |

|          |                            | 5.3.2.3 ExtractCex                                                 | 42 |  |  |  |  |

|          |                            | 5.3.2.4 Concretizable                                              | 42 |  |  |  |  |

|          |                            | 5.3.2.5 Refine                                                     | 42 |  |  |  |  |

|          | 5.4                        | Proof of Concept Implementation                                    | 43 |  |  |  |  |

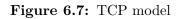

| 6        | App                        | plying Memory Models on Communication Protocols                    | 44 |  |  |  |  |

|          | 6.1                        | 6.1 Defining the Scope                                             |    |  |  |  |  |

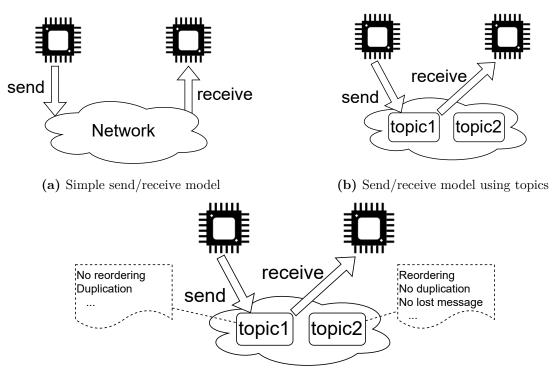

|          |                            | 6.1.1 Communication Behavior Patterns                              | 44 |  |  |  |  |

|          | 6.2                        | Modeling Behaviour Patterns                                        | 45 |  |  |  |  |

|          |                            | 6.2.1 Reordering Messages                                          | 46 |  |  |  |  |

|          |                            | 6.2.2 Duplicating Messages                                         | 46 |  |  |  |  |

|          |                            | 6.2.3 Losing Messages                                              | 47 |  |  |  |  |

|          |                            | 6.2.4 Broadcasting Messages                                        | 47 |  |  |  |  |

|          |                            | 6.2.5 Sending Synchronously                                        | 47 |  |  |  |  |

|          |                            | 6.2.6 Blocking Reception                                           | 47 |  |  |  |  |

|               | 6.3   | Exten  | ding the Standard Model             | 48        |

|---------------|-------|--------|-------------------------------------|-----------|

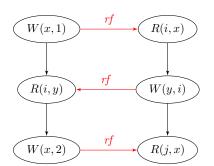

|               | 6.4   | Applic | cability of the Approach            | 48        |

|               |       | 6.4.1  | User Datagram Protocol (UDP)        | 48        |

|               |       | 6.4.2  | Transmission Control Protocol (TCP) | 50        |

| 7             | Con   | clusio | n                                   | 52        |

| $\mathbf{Li}$ | st of | Figure | es                                  | <b>54</b> |

| Bi            | bliog | graphy |                                     | <b>54</b> |

# **Kivonat**

A kritikus hardver-szoftver rendszerek formális verifikációja egyre több területen elvárás. Emberéletek múlnak programok hibamentességén, és emiatt teljesen biztosnak kell lennünk abban, hogy soha nem fognak meghibásodni.

A gyengén rendezett kommunikációs formák jelentik az egyik legnagyobb problémát, amivel a state-of-the-art verifikációs eszközök is küzdenek. A látszólag tetszőleges átrendeződések kezelhetetlenül naggyá teszik az állapotteret a konvencionális eszközök számára.

Jelen dolgozatomban egy áttekintő elemzést nyújtok a párhuzamosság hatékony kezelésére képes verifikációs eszközökről, mind a szekvenciális, mind a gyengén rendezett esetben (1). Implementálom az egyik legjobban teljesítő eszköz algoritmusát a THETA keretrendszerben, melyet a Kritikus Rendszerek Kutatócsoport fejleszt és tart karban (2). Továbbá javasolok egy olyan megközelítést, mellyel a gyakorlatilag végtelen állapotterű bemeneteket is hatékonyan lehet kezelni, valamint implementálom az algoritmus fő lépéseit (3). Végezetül, alkalmazom a memóriamodellezési elveket üzenetalapú kommunikációs protokollok modellezésére, ezzel kiterjesztve a fent bemutatott algoritmusok és megközelítések használhatóságát (4).

# Abstract

Formal verification of hardware-software critical systems is a necessity for an increasing number of applications. We trust the lives of people on the safety of computer software, and we have to be absolutely certain they will never fail.

One of the problems state-of-the-art verification tools struggle with is weakly ordered models of communication, both in the case of shared memory concurrency and distributed systems. The seemingly arbitrary reordering of accesses makes the state space unmanage-ably large for conventional approaches.

In this thesis, I survey the landscape of verification tools capable of performantly handling parallelism, both in the case of sequential consistency as well as weak memory ordering (1). I implement one of the best approaches in the verification framework THETA, a tool maintained by the Critical Systems Research Group (2). Furthermore, I propose a novel approach for handling practically infinite-state inputs for the weakly ordered memory models, and I create a proof-of-concept implementation of the main parts of the algorithm (3). Finally, I apply the memory modeling principles to message-based communication protocols, thereby widening the applicability of the algorithms and approaches shown before (4).

## Chapter 1

# Introduction

Safety critical hardware-software systems surround us in our daily lives. We rely on electronic brake systems to always slow down vehicles, automated power station management to never leave us without power and advanced collision avoidance systems to ensure no human error can lead to aviation catastrophes. However, developers of such systems can still be expected to make some mistakes, which could lead to faults causing many people to lose their lives or suffer outstanding monetary damages. The solution to this problem is tightly controlled quality assurance protocols, one part of which is to *verify* that the system will never find itself in an *unsafe* state under certain circumstances.

There are many methods of verifying safety. In the recent past, the most prominent technique has been testing, i.e., playing out scenarios with the system under test and comparing its responses to predetermined ones. While effective at catching common bugs, it is almost never exhaustive, meaning a proof of safety cannot be created via testing. In the scope of this paper, I deal with *formal verification*, which is a mathematically precise way of reasoning about a system's behavior. It is capable of both reporting bugs and capturing a proof a safety, but its performance overhead has been prohibitive of its use in the past. However, with the ever-growing pool of compute resources and the advancement of verification algorithms, its industrial use is starting to take hold and slowly replace (or at least complement) testing.

One of the techniques employed by formal verification is model checking [19], which uses a formal representation (a model), and by enumerating all its reachable states from some initial configuration, reason about its unsafe states. This method would solve all verification problems, as having access to the network of reachable states, any property over the state space would be trivial to check. However, in a general sense, this problem is undecidable: e.g., there cannot exist an algorithm that would determine whether any program terminates [42]. The discrepancy comes from the nature of the state space: it is not guaranteed to be finite, and in most real life cases, even finite-state systems have unmanageably large state spaces. Consider a simple program having two 32-bit integer variables. As each variable could have a possible  $2^{32}$  different values, the size of the state space of the program would be  $2^{32+32}$ , which would take up at least 18 exabytes of space given a very efficient 1 byte-per-state data structure. This phenomenon is called state space explosion [20], and most development effort towards model checking concentrates on the solution to this problem.

One possible solution to state space explosion is to employ *abstraction*, which partitions the concrete state space into groups that behave similarly. Using this method, the state space can become manageable and therefore verification may be feasible. However, the level of

abstraction has to be fine-tuned so that it allows the efficient verification of the system while preserving enough information to not produce false alarms – which might be provided by a continuously refined abstraction level in a solution such as the Counterexample-Guided Abstraction Refinement (CEGAR) technique [18].

While abstraction solves many of the problems of conventional model checking, a new source of complexity arises when asynchronous components work together in a system, such as concurrent programs or distributed systems. Special techniques have to be employed to deal with this behavior, as the naive way of enumerating all interleavings of the parallel components cause the state space the explode. While partial order reduction (POR [26]) has been extensively used to combat this, recent work has shown that an *axiomatic* approach [7] works better at exploring states of concurrent programs. This is especially true for programs where memory access is not sequential by default, i.e., the order of instructions need not reflect the order of their apparent effects. In this case, the rules of the *memory consistency model* give the axioms, which guide the state exploration.

While many tools use the axiomatic approach to verify concurrent programs with weak semantics [7, 32, 21], it is usually complemented by another well-established verification technique such as stateless model checking [32], or bounded model checking [21]. However, no such solution exists that combines axiomatic verification with abstraction-based model checking – and furthermore, the aforementioned tools mainly concentrate on verifying software, rather than general parallelised architectures such as distributed systems.

In this thesis, my presented contributions are as follows:

- I I survey and present the state of the art concerning software verification over axiomatic memory models

- **II** I implement a customized version of the algorithm used by one of the best state-of-the-art verification tools

- **III** I develop and implement an effective, abstraction-based state space exploration technique for handling axiomatic verification of concurrent software

- ${\bf IV}$  I show an application of the Cat [8] memory modeling language to network-based communication protocols

The structure of the thesis is as follows: in Chapter 2 I introduce the necessary background the rest of this thesis builds upon. In Chapters 3-6, I elaborate on the four main contributions of my thesis (see above). Finally, in Chapter 7 I conclude the thesis by summarising its main points and observations.

# Chapter 2

# Background

This report builds upon the theories and findings of many fields of computer science, including embedded programming, formal software verification, memory modeling, concurrent software design and distributed systems. Some of these fields view the same topics slightly differently, e.g. software verification presumes a formal, mathematical model for the input program, while embedded programmers usually use the much lower abstraction level of source code to reason about properties of the software. This necessitates establishing the basis of the presented work to prevent misunderstanding among experts in these fields. This chapter introduces such concepts and defines their interpretation as used in the context of this work.

### 2.1 Safety-Critical Systems

If a hardware-software system was designed for a small selection of well-defined tasks, it is generally referred to as an *embedded system*. Such systems are not adept for generalpurpose use, as their in- and outputs are often limited, and their software is seldom modifiable with the rare exception of program upgradability. *Embedded systems* can fulfil many kinds of tasks, ranging from operating the electrical windows on a car to performing complicated protocols for mid-air collision avoidance in airplanes (such as the Traffic Alert and Collision Avoidance System, *TCAS*), or providing a safety shutoff system for a nuclear plant.

Failure of an embedded system might be a minor nuisance or a serious safety problem, depending on the context of the application. If an electrical window fails on a car, the worst that can happen is some discomfort until the faulty unit is repaired or replaced – but failure of the TCAS might result in the collision of two airplanes where hundreds of lives are at risk. Any system that is designed to perform tasks where malfunction could lead to harm (physical or monetary) is classified as a *safety-critical system*.

Depending on the level of tolerable risk, a safety-critical system can be classified, e.g., according to *Safety Integrity Levels* (SIL) [30]. Several qualitative and quantitative measures are in place in such standards to mitigate dangerous failures, such as a controlled development workflow, thorough quality assurance and safety evaluation. For software components, the most widely used technique to assess safety is testing, i.e. running the program with defined sets of inputs and analyzing the outputs. This is not a definitive proof, as for untested inputs we cannot evaluate the behavior, but if the testing methodology is thorough enough, we can qualify the software as *probably safe* for the desired

safety integrity level. To aid testing, formal methods such as model checking [19] (also see Section 2.2) and formal test generation [16] can be used, which are often too complex to be used on their own, but can support conventional testing methods.

With recent years' advancements, even safety-critical systems reached the point where scaling up in performance is next to impossible if only a single core is utilized [39]. The next logical step is to introduce multi-processor chips that can use smarter workload management to overcome the need for computing power. However, with multi-processor architectures and multi-threaded programs, the complexity of embedded systems surpasses the verification power of conventional testing, mainly due to the inherent nondeterminism of multi-threaded programs. When a program is strictly run on a single-core processor, it is relatively easy to guarantee that for a single set of inputs, the output of the program will always be the same. Therefore, it is enough to test each input set once, and assess the execution's results. With multi-threaded programs, an otherwise deterministic program can still produce different results based on timing differences among the processors, which cause different sections of the program to overlap in execution. Hence, testing is even less effective at proving safety, and a more formal method is often required.

A similar problem arises when instead of running on a multi-core processor, programs offload certain tasks to other participants in some network. This is the model of *distributed systems*, where in addition to the already high complexity of verifying separate subsystems on their own, their cooperative behavior needs to be verified as well. In some aspects, concurrent program execution and cooperative distributed systems operate under the same pretenses, but the way information is exchanged among them is inherently different.

### 2.2 Formal Software Verification

Formal software verification is a way to mathematically prove or disprove certain properties of an input program. Such properties might include *memory safety* (detecting use-afterfree and other memory allocation problems), *reachability* (detecting if an unsafe state is reachable) or *termination* (detecting if the program will terminate in all its executions). In the context of this work, safety properties are always assumed to be *reachability* related, with a single unsafe state in the program.

Formal software verification often employs model checking [19], a technique that enumerates states of the input program and reasons about the properties of the states. For reachability-type queries, it is necessary to know whether the state marked as unsafe is reachable from the initial state(s) within a finite number of steps – if such a path exists, the program is deemed unsafe and safety cannot be guaranteed. In practice, generating all states of an input model is often infeasible, as even a single 32-bit variable will create  $2^{32}$  different states according to its value. This phenomenon is called state space explosion [20], and counteracting it is required for any practically useful model checking algorithm.

A theoretical problem that verification tools have to face is the inherent *undecidability* of the model checking problem. Consider an arbitrary input program and an unsafe state at its exit point. To prove the (un)reachability of said state, the program's termination property has to be decided – which is proven to be undecidable [42]. This means, that any model checking algorithm will either be *incomplete*, i.e. some inputs will result in an *UNKNOWN* classification, or will produce *false* results in the form of *false alarms* and *missed bugs*.

A further problem of such algorithms is bridging the gap between the different abstraction levels in the verification workflow. Embedded programs are usually written in C or a sim-

ilar high-level language, where concepts such as variable scopes, procedures and pointers make the lives of programmers easier, abstracting away the single instructions that will be generated by the compiler. However, the rich toolset of high-level languages greatly hinder the reasoning power of any formal method, as a formal model of the language semantics would be required. This is hard for some languages, and impossible to create for others: e.g. in the case of C++, the grammar is undecidable, i.e. there cannot exist any program that parses all C++-compliant code correctly<sup>1</sup>. To overcome these kinds of problems, the input programs are first transformed into a formal model, which can be done separately, as a pre-processing step, either by hand or in an automated way. However, it is important to keep in mind that the verification result of the model checking algorithm will only be valid for the formal model that served as its input, and not necessarily the source program – for that, verifying the result against the program's code might be necessary.

One such formalism is called a *Control Flow Automaton* (CFA) [13], which is mainly used to model programs.

**Definition 1 (Control Flow Automata).** A control flow automaton is a tuple  $CFA = (V, L, l_0, E)$ , where:

- V: A set of variables

- L: A set of locations, representing the program counter (PC) in the program

- $l_0 \in L$ : The initial location

- E ⊆ L × Ops × L: Directed edges in the CFA, describing the set of operations to be executed when the program advances to a new location

- $op \in Ops:$  An assumption of a predicate over V asserting its truth (i.e. an execution is only legal if the predicate is fulfilled), or an assignment of a new value to a  $v \in V$ . A special kind of assignment has the form havoc v, which assigns a non-deterministic value to v.

An execution of a CFA is a path over the directed edges E, starting from  $l_0$ , where at least one variable assignment exists that satisfies all assumptions of this path. Note that in the CFA, we use non-constant variables, which means multiple values can be assigned to a variable in a single execution. To keep track of variable values, *indexed constants* are used, where the index is increased with each assignment to the same variable. Assumptions and expressions always use the most recent *indexed constant*.

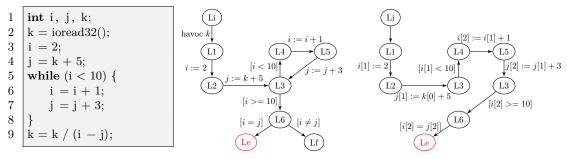

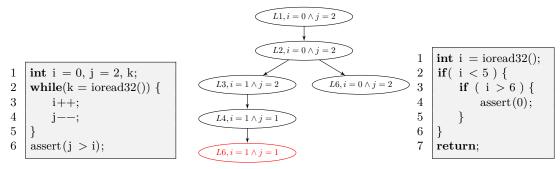

Consider the example in Figure 2.1. The program in Figure 2.1a reads a non-deterministic number k, then does several calculations over the variables i, j, k that includes a potential division-by-zero in line 9. This program is transformed into a CFA in Figure 2.1b, which includes an error location Le that represents the division-by-zero case, and a final location Lf which represents the successful termination of the program. An arbitrary path in this CFA leading to Le is presented in Figure 2.1c, which also shows the use of *indexed constants*. This format is called *Static single assignment*, as every indexed constant is assigned exactly once, meaning each value is invariant throughout the execution. Figure 2.1d shows the path feasibility query as a satisfiability formula, which can be given to an SMT-solver that can determine whether the path is a legal execution. In the presented case, there is a clear contradiction in the expressions over i[2]: if i[1] is 2 then i[2] := i[1] + 1 means i[2] must be 3 – which contradicts the i[2] >= 10 assertion. This means the path is not a feasible execution, and we have not yet determined the safety of the program.

<sup>&</sup>lt;sup>1</sup>https://blog.reverberate.org/2013/08/parsing-c-is-literally-undecidable.html

(a) C program with pos- (b) Control Flow Automaton (c) Static single assignment form of sible div.-by-zero

for Figure 2.1a

a path in Figure 2.1b

| i[1] = | $2 \wedge j[1] = k[0] + 5$ | $5 \wedge i[1] < 10 \wedge i[2]$ | $2] = i[1] + 1 \land j[2] =$ | $= j[1] + 3 \wedge i[2] >= 1$ | $0 \wedge i[2] = j[2]$ |

|--------|----------------------------|----------------------------------|------------------------------|-------------------------------|------------------------|

|--------|----------------------------|----------------------------------|------------------------------|-------------------------------|------------------------|

(d) SMT-expression of the path in Figure 2.1c

Figure 2.1: Mapping a program to a CFA

Note that while not explicitly shown, every *havoc* operation causes the index of the constant to increase, but nothing gets assigned to this constant. This means that the solver is free to choose any assignment, as long as it satisfies all other assertions that refer to this constant. Also, note that the example CFA in Figure 2.1b is not a correct mapping of the program in Figure 2.1a, as the values of the variables are entirely unbounded. This can be problematic if a path is found where the SMT solver reports the query as *satisfiable*, while in practice one of the variables would have wrapped around before reaching a value in the counterexample, making the path infeasible. This is a well-known limitation of SMTbased model checking, as fix-bit-width types cannot easily be mapped to mathematical integers. In the context of this work, best-effort practices are performed to counteract this phenomenon, namely, each havoc automatically implies an assumption over the variable's bounds (e.g. a C-like integer i will have an assumption that  $-(2^{31}) \leq i \leq 2^{31} - 1$ ); and each unsigned integer type will wrap around when an out-of-bounds value is assigned to it, using modular arithmetic (e.g. a simple addition of the unsigned variable u := u + 1 will be mapped to  $u := (u+1) \mod 2^{32}$ ). As signed overflow is undefined in the C standard (and most other programming languages) [31], that case is unhandled and the values might fall out-of-bounds. A correct solution to this problem is to use bitvector arithmetic instead of integer arithmetic, but the implied performance overhead warrants the presented more performant approximation.

As we saw in Figure 2.1, the arbitrarily chosen path was not a feasible execution. However, that does not mean the program is safe – in fact, all paths would have to be checked first, to see if any produce the undesired division-by-zero problem. It is easy to see that due to the loop in the program, there are an infinite number of paths – to solve this model checking problem in a finite amount of time, many different approaches exist, but most of them fall into the following categories:

- Bounded Model Checking (BMC) Starting from the initial state(s), check if an unsafe state is reachable within an expanding number of steps [15]

- k-Induction Starting from the unsafe state(s), check if a safe state can be an expanding number of steps before any of the unsafe states [23]

- Explicit-State Model Checking Mapping the states and transitions to an abstract state space using explicit-valued abstraction [29]

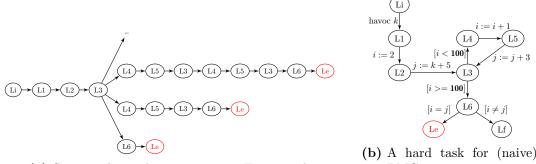

(a) Some paths to the error state in Figure 2.1b

BMC

Figure 2.2: Bounded Model Checking example and limitations

Counterexample-Guided Abstraction Refinement (CEGAR) – Mapping the states • and transitions to an abstract state, then refining the abstraction in subsequent iterations until a feasible counterexample is found, or safety is proven [18]

These techniques are generally used for different applications, e.g. BMC will usually find bugs the fastest but will not terminate if the state space is too big, while k-Induction is often capable of proving safety while not finding actually reachable unsafe states. Abstraction based techniques can be more complex and therefore slower, but they can both find bugs and prove safety relatively effectively. In the context of this work, I examined algorithms based on the BMC-approach, while the proposed new technique shows the abstraction-based state space exploration used by CEGAR. Therefore, I shall introduce these two approaches in detail below.

#### Bounded Model Checking (BMC) 2.2.1

As stated above, Bounded Model Checking (BMC) starts off with one or more initial states as the root of a tree graph, then repeatedly adds new states to the existing ones along transitions of the state space in a breadth-first-search (BFS) manner, i.e. all Nfar states are added to the graph before any of the (N + 1)-far states. After reaching the upper bound of the analysis k, the graph is transformed into a satisfiability-modulotheory (SMT) expression using the following recursive rule: the expression at a node is the conjunction of its state expression and the disjunction of expressions in subsequent nodes. This means that any junction will create an Or expression, and any paths will create an And expression. If this expression and the expression of the unsafe state are satisfiable together, the program is faulty as the unsafe state is reachable within this k-bound. Otherwise, the analysis continues building the graph with a new bound k' > k.

Take the example in Figure 2.1. The BMC algorithm will try to enumerate increasingdepth paths that end in the error location. The first few such paths can be seen in Figure 2.2a, but looking at the program in Figure 2.1a, these paths will be infeasible, as the value of i has not yet reached 10, i.e. the exit condition of the loop has not yet been fulfilled. After 8 iterations, and at a depth of 30, a feasible path will be found - if we assign -19 to k, the division will fail to due to the divisor being 0. Therefore, the program can be reported as *unsafe*.

Now consider the program in Figure 2.2b. The only difference to Figure 2.1b is the exit condition of the loop – instead of 8 iterations, the program must take 98 iterations before exiting the loop. For a naive BMC implementation, this means that it has to evaluate

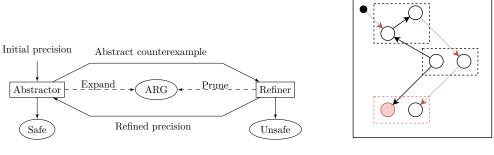

Figure 2.3: The CEGAR loop

Figure 2.4: An ARG

97 infeasible paths before the counterexample is found. While possible, it might take a long time – and in the meantime, no proof of safety is possible as only specific traces are evaluated, rather than the whole program.

This trait of BMC (i.e. evaluating concrete traces rather than an abstract model) is both the source of its limitations, and its main advantage – if there is a bug, BMC is capable of finding it quickly, given it is not buried too deep in the program. This makes it appealing to use when a guarantee of safety is not required, but there is an incentive for finding bugs.

#### 2.2.2 Counterexample-Guided Abstraction Refinement (CEGAR)

As opposed to BMC, CEGAR is a tool both for proving safety and finding bugs. While implementations of CEGAR are generally slower than BMC-based tools due to the algorithmic overhead; CEGAR can handle a superset of the tasks that BMC could solve (see Section 2.2.2.3). This means that the verification power of CEGAR is at least as big as that of BMC.

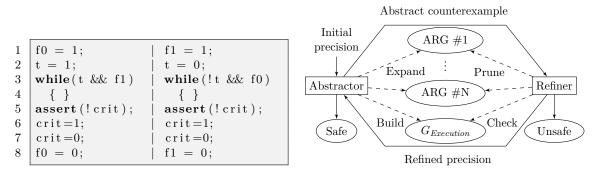

#### 2.2.2.1 A Generic CEGAR Loop

CEGAR is a highly configurable verification algorithm [18], where the main product of the workflow is the *Abstract Reachability Graph* (ARG) [12]. The ARG is an overapproximation of the reachable state space, meaning a reachability in the concrete model implies reachability in the ARG, but not necessarily vice versa. This property can be seen in Figure 2.4: even though the filled-in error state is seemingly reachable if only the abstract states (denoted by rectangles) are taken into account, there is no actual path among the concrete states that could lead to the error state. Therefore, this level of abstraction is too high, and a more refined version is necessary.

A notable feature of ARGs is state coverability: if a state is found to be *covered* by another state, i.e. there is another state whose truth value is implied by the truth value of the current state (e.g.  $S_1(a = 2, b = 3)$  implies  $S_2(a = 2)$ , therefore  $S_2$  covers  $S_1$ ). In this case, there is no need to expand the current state any further, as any observed behavior will also be observed by the *covering* state. This is a vital tool for combating state space explosion, as this means that covered states are handled only once. For example, if a program contains a loop that does not influence the reachability of the error state (e.g. waiting for an input), the only state we are interested in is the exit point of the loop – any in-between states are covered-by the loop header state, and therefore not expanded further.

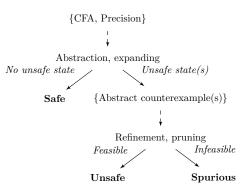

Figure 2.5: The CEGAR workflow

To achieve this continuous abstraction-then-refinement workflow, CEGAR works in a loop, as seen in Figure 2.3. This loop consists of two main algorithms working together: the abstractor and the refiner. The abstractor takes a precision describing the level of abstraction and the input model, and either creates a new ARG or expands the previously created, and pruned back ARG. This method is useful if a path is only found to be infeasible after a few feasible steps, and therefore the beginning of the ARG needs not to be re-created. When an ARG is ready, the abstractor checks whether an unsafe state is reachable, in which case the program is reported as *safe*. Note that safety is provable over an abstract state space, as it is always an over-approximation of the concrete state space and therefore the lack of an unsafe, abstract, reachable state implies the lack of an unsafe, concrete, reachable state as well.

If the created ARG does contain an unsafe state, the abstractor creates one or more *abstract counterexamples*, which are paths in the ARG leading to an unsafe state. These abstract counterexamples are then passed onto the refiner, which has multiple tasks: firstly, trace feasibility is evaluated (i.e. is at least one abstract counterexample concretizable, in which case the program is reported as *unsafe*). Then, if the counterexamples are infeasible, a new precision is created that is less abstract than the last one. Furthermore, the ARG is pruned back to the point where it became infeasible, then control is given back to the abstractor, where this abstraction-refinement cycle starts again.

The state of the algorithm after a single iteration of the CEGAR loop can have three values: *safe*, *unsafe* and *spurious*, as seen in Figure 2.5. The algorithm also produces proofs by default: for safety, a completely expanded ARG without an unsafe state suffices; and a feasible (concretizable) trace serves as the counterexample that shows the path to the bug in the program.

#### 2.2.2.2 CEGAR Configuration Options

The CEGAR loop, as seen so far, is a declarative specification of the verification algorithm, i.e. only outcomes are specified and not the actual way to achieve said outcomes. This is due to the inherent configurability of CEGAR: as long as the parts are compatible with each other, many aspects of the algorithm can freely be swapped to other techniques fulfilling the same purpose.

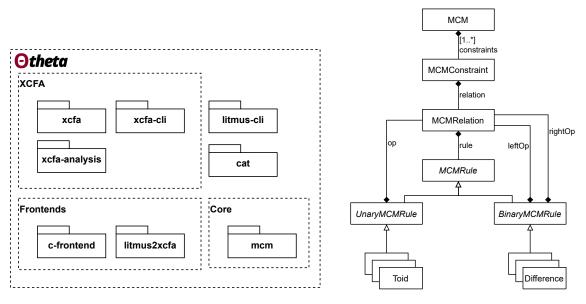

As the possibilities are (almost) endless in terms of configurability, I only present the options provided by THETA<sup>2</sup>, an open-source, generic and modular model checking frame-

<sup>&</sup>lt;sup>2</sup>https://github.com/ftsrg/theta

work developed at the Critical Systems Research Group of Budapest University of Technology and Economics [40]. In the context of this report, I developed the proof-of-concept implementations of the presented algorithms in THETA. This choice is in part justified by the maturity of the framework (the implementation has been validated on thousands of input models, e.g. in the SV-COMP 2022 software verification competition<sup>3</sup>), and also based on my previous contributions to the framework, which are prerequisites for the work presented in this report. All implementation-specific details are published in [28] – I will only introduce those relevant to my work.

THETA implements the CEGAR loop with complete modularity in mind. It provides several built-in options for each swappable component, as well as an easy way to define custom ones. The two (arguably) most important ones are the *abstract domain* and the *refinement algorithm*.

#### 2.2.2.2.1 Abstract Domain

The *abstract domain* specifies the basis of the abstraction, and by default, there are two *pure* domains implemented in THETA: the *explicit value* domain and the *predicate* domain. The latter is further divided, based on the way multiple predicates are handled inside a single state – there are *cartesian predicate abstraction*, *boolean predicate abstraction* and *split boolean predicate abstraction* domains. As previous results showed that software verification does not usually benefit from boolean predicate abstraction [28], I only focused on the *explicit* (EXPL) and *cartesian predicate* (PRED\_CART) abstraction domains.

**Definition 2 (Abstract Domain).** Formally, an abstract domain is a tuple  $D = (S, \top, \bot, \sqsubseteq, expr)$  [28], where:

- S: Lattice of abstract states (possibly infinite)

- $\top \in S$ : Top element

- $\bot \in S$ : Bottom element

- $\sqsubseteq \subseteq S \times S$ : Partial order over the lattice S

- expr: A mapping from an abstract state to an actual data state (i.e. an expression)

To define an abstract domain, one has to give a mapping for each member of the tuple D.

**Explicit Domain** The *explicit* abstraction domain defines the current abstraction precision as a set of *tracked* variables, i.e. variables whose values are of interest to us. Formally, the explicit domain can be defined as follows:

- S: A variable assignment of each *tracked* variable to a value of its domain, extended with top (arbitrary value) and bottom (no assignment possible) elements.

- $\top \in S$ : No specific value is assigned to any of the tracked variables.

- $\perp \in S$ : No assignment is possible to the tracked variables.

- $\sqsubseteq \subseteq S \times S$ :  $(s_1 \in S) \sqsubseteq (s_2 \in S) \iff (s_1 = s_2) \lor (s_1 = \bot) \lor (s_2 = \top)$

- expr: The conjunction of the equality expressions for each tracked variable and their value

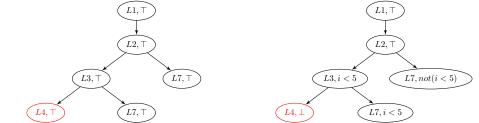

(a) Positive example for (b) ARG of Figure 2.6a, using line numbers (c) Negative exam-EXPL as CFA locations, tracking *i*, *j* and *k* ple for EXPL

(d) ARG of Figure 2.6c, using line numbers (e) ARG of Figure 2.6c, using line numbers as CFA locations, tracking i as CFA locations, tracking i < 5

Figure 2.6: Advantages and disadvantages of the EXPL domain w.r.t. PRED\_CART

Note that when applying CEGAR on a CFA, the locations of the CFA are always explicitly tracked, as to always have a 1: N relation between locations and states in the ARG.

The *explicit* abstraction domain also specifies a *maxenum* value, which is an upper bound on the enumeration of values to a variable in a single step – which can be useful if the domain of a variable is infinite or very large. Consider the program in Figure 2.6a: tracking the value of k is next to impossible, as it is always assigned a 32-bit non-deterministic number. Enumerating all possible states leads to the state space explosion we are trying to avoid. Therefore, the algorithm does not try to assign a value to k in any of the abstract states in the ARG in Figure 2.6b, even though the precision would allow it – instead, k is kept at its top element. However, even without the value of k, the algorithm is capable of deciding the safety of the ARG: after just one iteration, the assertion fails. In this example, this abstract counterexample also corresponds to a concrete trace, and therefore the refiner will most likely report the program as *unsafe*.

**Predicate Domain** The *cartesian predicate* abstraction domain defines the current abstraction precision as a set of tracked (and ponated)<sup>4</sup> predicates. Formally, the cartesian predicate domain can be defined as follows:

- S: A conjunction of predicates

- $\top \in S$ : True

- $\bot \in S$ : False

- $\sqsubseteq \subseteq S \times S$ :  $(s_1 \in S) \sqsubseteq (s_2 \in S) \iff (s_1 \implies s_2)$

- *expr*: The conjunction of the predicates applicable to the current state

<sup>&</sup>lt;sup>3</sup>https://sv-comp.sosy-lab.org/2022/

$<sup>{}^{4}\</sup>mathrm{A}$  ponated predicate means the outermost expression cannot be a Not operator.

Consider the program in Figure 2.6c. If we tried to solve this reachability problem with the explicit domain, we would get the ARG in Figure 2.6d even at the maximal precision of tracking all (one) variables. The unsafe state is reachable in the ARG, and therefore the abstractor cannot classify the input as safe – even though it is evident from the program's source that the assertion would never be reached, due to the contradicting i < 5, i > 6 assumptions. However, we cannot assign concrete values to i throughout building the ARG, as i can take up almost  $2^{31}$  different values that would fulfil either criteria, and we can only evaluate one *if* statement at a time if the CFA contains different edges for them. (As a sidenote, this problem could also be solved by using large-block encoding (LBE) [14], but currently, THETA only supports a simple version of that).

In comparison, the cartesian predicate abstraction only needs the predicate i < 5 in the precision to deduce the safety of the program, as seen in the ARG in Figure 2.6e. Note the unsafe state in red: the ARG building algorithm correctly assigned the bottom element  $\perp$  to its abstract state, as there was a contradiction in the path – meaning the ARG is complete and lacks unsafe states, and therefore the program is *safe*.

An aspect of the abstraction that was previously left out is the *transfer function*. The transfer function T maps sets of abstract states to the tuples consisting of an abstract state, a list of operations and a precision  $(T: S \times Ops \times Prec \mapsto 2^S)$ . In practice, this determines the successor states of an abstract state in the ARG – which is a clear contradiction to the previous description of how an ARG is created (i.e. grouping concrete states together). While that was also a correct way of creating an ARG, it is not practical to create all concrete states just for being able to create abstract states out of it: instead, the transfer function is used to explore the abstract state space, and expand previously discovered abstract states. For example, given the EXPL domain, a precision tracking i, and an edge in the CFA assuming  $i > 0 \land i < 4$  between locations  $l_1$  and  $l_2$ ; the state  $s_0(l_1, \top)$  would have the following successor states:  $\{s_1(l_2, i = 0), s_1(l_2, i = 1), s_1(l_2, i = 2)\}$ .

Note that even though the transfer function assigns successor states to abstract states deterministically, the way these successor states are handled deeply influences the verification workflow: it is possible to visit and expand the first successor state in every instance, and therefore explore that state space in a depth-first manner (DFS), and it is also possible to visit all successors first before successors to those are visited and expanded (BFS). Any further combination of these techniques can also exist, such as an error-location-guided search (ERR), which will favor DFS more if the state is closer to the error location, but defaults to BFS otherwise [28].

#### 2.2.2.2.2 Refinement Algorithm

As we have seen in Figure 2.6e, the predicate i < 5 in the precision was enough to guide the abstraction algorithm towards discovering that the program is *safe*. However, the discovery of this predicate is not trivial, and it can come from two sources: either from the initial precision (e.g. all assumes in the model), or the refinement algorithm will have to discover it while refuting the abstract counterexamples.

There are many different refinement algorithms implemented in THETA, but the relevant distinction among them in the context of this report is the following:

- Single-counterexample refinement: a single counterexample is generated from the unsafe ARG, and refuting it provides the new precision for the abstractor

- Multi-counterexample refinement: every counterexample is generated from the unsafe ARG, and a combined refutation provides the new precision for the abstractor

#### 2.2.2.3 BMC Inside CEGAR

As mentioned above, CEGAR is at least as powerful of a verification tool as BMC, due to BMC being part of CEGAR. In order to justify this claim, consider the following:

- The CFA is extended with a counter c, which is increased after every statement in the model, starting with 0

- domain: EXPL

- initial precision:  $\{c\}$

- search algorithm: BFS

This configuration will mimic the BMC algorithm, as it enumerates all paths in the program following the value of c. If BMC can find a counterexample, this method will be able to find it as well – and if BMC runs out of enumerable paths and classifies the program as *safe*, this technique will arrive at the same conclusion as well.

### 2.3 Multi-Processor Architectures

Modern hardware architectures almost universally offer concurrent memory access in a relaxed way. This means that read and write operations do not have to execute sequentially, the memory controller is free to reorder them (respecting certain constraints) to increase performance. The rules for such relaxed accesses is described by a *memory consistency model* (MCM). The specification of MCMs evolved from textual documentation through small "Litmus-tests" describing forbidden outcomes to well-defined axiomatic formal specifications of the execution semantics [10, 7, 38].

### 2.3.1 Memory Consistency Models

Generally, a memory model of an architecture can either be *operational* or *axiomatic* [7]. The former uses elements of the hardware platform such as queues and buffers to explain certain behaviors on the target architecture, which makes it easier to implement the architecture directly in hardware, but hinders reasoning on the software side [38]. In contrast, an *axiomatic* memory model uses a declarative approach to forbid certain sets of relations over memory accesses [10]. This approach proved to be better for reasoning about possible executions of concurrent programs, and therefore most software verification tools employ an *axiomatic* model to provide information on the guarantees of the hardware architecture [5, 3, 2, 25, 21] or the programming language [32, 35].

One *axiomatic* memory modeling language is CAT [8], which has been created to specify memory models for HERD [7] but has since seen widespread adoption due to its succinctness and expressivity.

The CAT language uses the notion of *candidate executions* to model possible executions of a program. A candidate execution is a directed, labelled graph, where each node corresponds to an *event* and is labelled by the specific *event sets* it belongs to; and each edge corresponds to a binary *relation* defined over the events. Event sets and relations come from both a predefined list of built-in elements, as well as the memory model.

#### 2.3.1.1 Event Sets, Relations and Constraints

The predefined event sets consist of the following [8]:

- W: write events

- R: read events

- M: memory events  $(M = W \cup R)$

- IW: initial writes stemming from the initial memory state

- FW: final writes observed at the end of test execution

- B: branching events

- RMW: read-modify-write events

- F: fence events

- *XYZ*: specific fence events from the architecture (such as MFENCE, FENCE and SFENCE for x86)

Derived event sets can be created by applying set operations over existing ones, such as union, intersection and difference. Furthermore, the (possibly filtered) Descartes-product of event sets can lead to *relations*. Some relations are predefined as follows [8]:

- po: program order

- addr: address dependency (the target event's memory location depends on the source read's value)

- data: data dependency (the target write's value depends on the source read's value)

- ctrl: control dependency (the target event is found in a branch controlled by an assumption depending on the source read's value)

- rmw: read-exclusive write-exclusive pair: the target exclusive write is a successful operation matched with the source exclusive read; or atomic RMW instructions

- amo: relate the read and write events of atomic RMW instructions

- id: identity (relate each event to itself)

- loc: same-location (relate all event-pairs that touch the same memory location)

- ext: external (relate all event-pairs that reside in *different* threads)

- int: internal (relate all event-pairs that reside in *the same* thread)

- rf: read-from (the target read's value is taken from the source write)

- co: coherence order (a total order of same-location write events)  $^{5}$

Derived relations can be created by applying one or more of the following operators over existing ones:

- Complement

- Domain

- Identity closure

$<sup>^5 \</sup>rm While \ CAT$  in itself defines co as a derived relation, it is a vital element of every execution and therefore I elevate it into this list

(d) Last value is 2, Read receives 0

(e) Last value is 1, *Read* receives 0

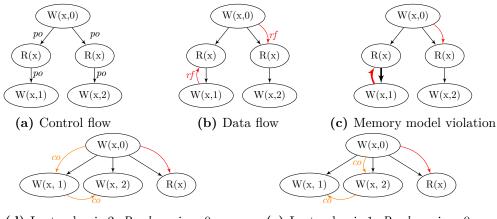

Figure 2.7: Candidate executions

- Inverse

- Reflexive transitive closure

- Transitive closure

- Range

- To ID

- Sequence

- Union

- Difference

- Intersection

Finally, relations can be constrained to be *(ir)reflexive*, *(non-)empty* or *(a)cyclic. Candidate executions* can be checked against the memory model specification to decide if they are *consistent* or *in violation* with the candidate. For example, against the specification that no *Read* on a given thread shall receive a value from a later *Write* on the same thread (any path  $(po | rf)^+$  is acyclic), the example *candidate execution* in Figure 2.7c is in violation of the memory model. However, if a *candidate execution* is indeed *consistent*, it becomes an *execution graph*, describing an observable outcome on the given architecture.

Note the lack of other primitives on the execution graph. By populating the po and rf relations the necessary control and data flow is fully defined, and no further relation is necessary – most notably, the coherence order co [7, 21] (or modification order [32]), i.e. the total ordering of same-location Write events, is entirely superfluous. Consider the two candidate executions in Figures 2.7d and 2.7e, where this relation is not omitted. In both cases, the *Read* will read 0 from memory, but the order of the *Write* events differs. The outcome and overall execution of the program is not influenced by these differences other than the final observable value in memory. However, as the two executions are not the same graph, both variants will be produced when enumerating the possible *candidate executions.* Unless the state of the global memory is ever needed to be queried, it is enough to determine for each *Read* event the set of *Write* events it might receive data from. This does not mean that any derived relation that uses *co* as one of its operands will have to be completely re-written, but rather that we can simply leave *co* as unspecified with a few constraints: as long as there is a *co*-order that relates every same-location pair of writes in either in exactly one way (i.e. if elements a and b are same-location writes, either co(a, b)or co(b, a) is true, but not both), the execution is feasible.

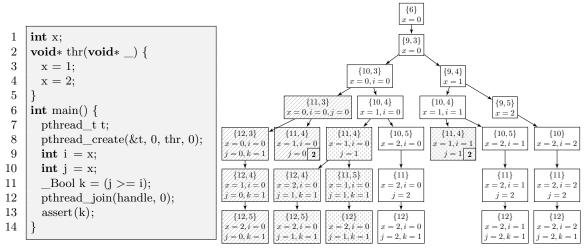

(a) Concurrent program test- (b) State space of Figure 2.8a, using tuples of line numbers as ing sequentialitylocations (States with bold numbers are not fully expanded)

Figure 2.8: State space exploration based on naive interleaving semantics

### 2.4 Analysis of Multi-Threaded Programs

Concurrent software verification algorithms also fall into two categories, depending on the execution semantics they employ. The *interleaving* semantics uses overlapping traces of the threads in the concurrent program to explain how it executes. This approach, when used naively, does not scale well due to the large number of possible unique executions. This is partially solved by utilizing e.g. *partial order reduction* (POR) [26], which significantly reduces the number of necessarily explored executions. In contrast, the *declarative* semantics of concurrent program executions uses partial orders to explain a specific execution. The *candidate executions* introduced above are examples to such a semantics, as the *po* and *rf* relations partially order the statements and yield a well-defined single execution of the program [7]. This *declarative* semantics has been shown to perform better on weak memory than the *interleaving* semantics over sequential memory, when implemented in model checking algorithms [6].

#### 2.4.1 Interleaving Semantics

The naive way of dealing with concurrency is to strictly follow the definition of asynchronous systems, i.e. any of the threads may execute at any point in time, meaning every possible total order of the instruction has to be explored. This technique employs *naive interleaving semantics*.

Consider the example in Figure 2.8a (note that based on the C standard, a global variable will be initialized to 0, if no explicit value is assigned [31]). The main thread starts a worker thread, which writes two values to x, while the value of x is read twice. As the value of x increases monotonically, we assert that the latter read's value shall be at least big as the former's. We store this in a boolean k. If we tried to enumerate all executions based on the naive interleaving semantics, we would get the state space in Figure 2.8b – there are 10 different executions that can take place, as the 3 + 2 operations between the start and end of the worker thread give rise to 10 total orders. However, if we examine the outcomes of the different executions, the set of possible end values is way smaller: x is always 2, j is always bigger than i and k is therefore always 1. Even though i and j can

Figure 2.9: POR-based state space of Figure 2.8a, using tuples of line numbers as locations (main thread executes first)

take up any one of the values from the set  $\{(0,0), (0,1), (0,2), (1,1), (1,2), (2,2)\}$ , this is still only 6 possible outcomes instead of the 10.

To explain this behavior, let us examine the three branches of the state space tree marked with patterns. In these executions, the values to i and j were decided early on, as the main thread progressed more than the worker thread. In theory, this would eliminate the need for further analysis, as any further action on either thread is independent of the other – x will be increased further, but no operation will use its value; and k is never used in any of the global memory accesses. However, the naive interleaving approach had to explore these subexecutions as well because it had no way of determining which operations would influence the final outcome and which ones would not.

An intuitive step to take is to discover independent pairs of transitions in the model, and forbid the exploration of both total orders. This technique is called *partial order reduction* (POR) [26], and it is widely used in the verification of concurrent systems (Even though there is a specialized version of POR called *dynamic partial order reduction* (DPOR) [24], which is shown to be more optimal, introducing and implementing that algorithm falls outside the scope of this work).

Consider the same input program in Figure 2.8a. If we apply POR based on a global-local partitioning of the transitions, where every transition touching a global memory object is considered dependent on each other, we get the state space in Figure 2.9. In this case, state space exploration was *optimal*, as each explored total order yielded a different outcome, and no possible outcome was left out.

Even though the presented example showed the POR algorithm to be *optimal*, this is not the case in every input program. For example, there could be another, totally independent y global variable, and two threads performing the same operations over y as over x – in this case, all total orders would have to be explored among accesses to the global variables as well, which would yield a suboptimal exploration. There are techniques mitigating this behavior (e.g. in [1], the authors have shown that there is an optimal DPOR, and also gave an example for such an algorithm), but the presented naive POR cannot deal with this problem.

(a) Abstract execution graph of Figure 2.8a (b) A concrete execution from 2.10a

Figure 2.10: Program verification based on declarative semantics

#### 2.4.2 Declarative Semantics

To showcase the differences between the interleaving and declarative semantics, let us look at the same problem in Figure 2.8a. To generate the declarative state space of the program, an *abstract execution graph* is necessary – which is similar to a candidate execution, but Reads are not limited to a single rf-edge, and only po- and rf-edges are present. The semantics of such a construct is the following: all executions are *observable* which stem from a consistent candidate execution that is a subgraph of the abstract execution graph, and for which a satisfying total co order exists over same-location writes. Such an abstract execution is shown in Figure 2.10b.

Note that in this case, state space exploration is optimal by default: after the abstract execution graph is built (which is interleaving-free, and therefore can be built in a single-pass over the operations in the program), only different, and consistent execution graphs are enumerated.

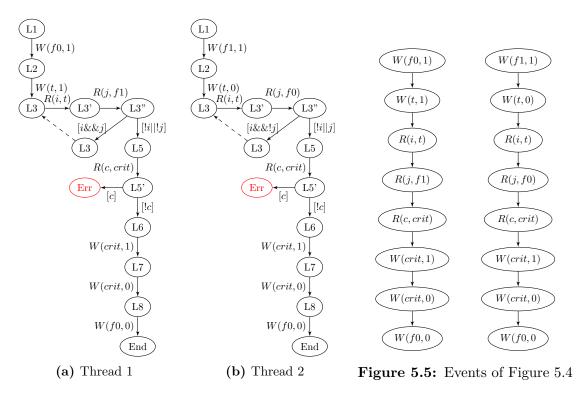

### 2.4.3 Multi-Threaded CFA

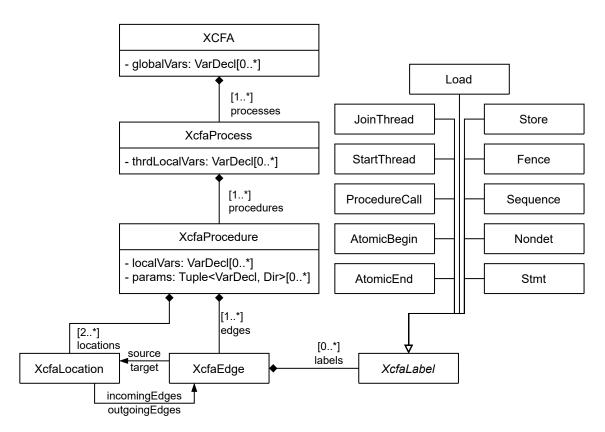

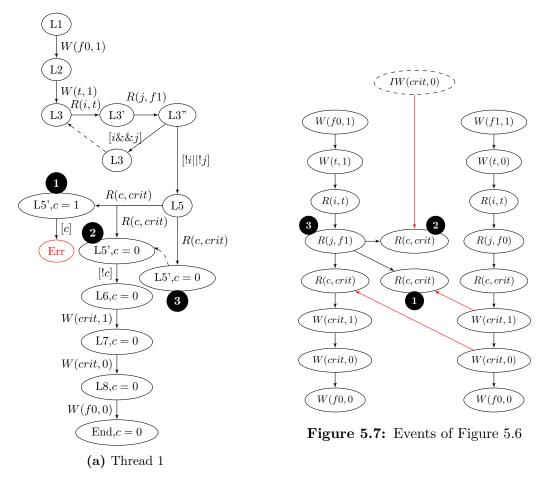

In order to verify multi-threaded programs, a formalism supporting multi-threading is also necessary. As with single-threaded programs, a formalism encoding control-flow in the form of a program counter-like construct is advantageous – therefore, the basis of the chosen formalism is still a control flow automaton (CFA) [13]. However, this formalism has been extended in the following ways, giving rise to the eXtended Control Flow Automata (XCFA): **Definition 3.** eXtended Control Flow Automata (XCFA) An XCFA is a tuple  $XCFA = (V_g, P)$ , where:

- V<sub>q</sub>: Global variables

- P: Processes, which are tuples  $P = (V_p, F, f_0)$ , where:

- $-V_p$ : Thread-local variables

- F: Procedures, which are tuples  $F = (V_l, CFA, P_{in}, P_{out})$ , where:

- \* V<sub>l</sub>: Local variables

- \* CFA: A conventional CFA (which can use  $V_g \cup V_p \cup V_l$  as variables), extended with the following operations:

- Function calls

- $\cdot$  Start thread *and* join thread

- · Atomic begin and atomic end

- · Store, Load and Fence

- \*  $P_{in} \subseteq V_l$ : Input parameter variables, which are assigned when the function is called

- \*  $P_{out} \subseteq V_l$ : Output parameter variables, which are returned when the function returns

- $-f_0 \in F$ : The main function of the process (execution starts here)

Semantically, an XCFA can either be static or dynamic. In the former case, only the starting set of processes can execute. In the latter case, the start thread and join thread operations manipulate the set of enabled processes. In both cases, the processes fire asynchronously.

Note that variables can either be assigned via normal assignments (as in a conventional CFA), or through *store* and *load* operations. In the context of this work, I assume total sequentality for assignments, and only apply the memory model for the analysis of the designated memory access instructions.

## Chapter 3

# State of the Art

My contributions presented in this thesis mainly concentrate on the efficient handling of parallelism, handling both the sequential and weakly ordered case. In this chapter, I introduce the state-of-the-art tools for handling concurrency in these cases. For the sequential case, I concentrate on the algorithms employing a form of CEGAR, as that falls the closest to the scope of my work; while for the weakly ordered case I introduce the most advanced *bounded* algorithms, due to the lack of a general solution covering infinite-state programs<sup>1</sup>.

### 3.1 Sequentially Ordered Concurrency

Most model checkers capable of verifying concurrent programs that employ a form of abstraction-refinement techniques use a pre-processing step to determine atomically executable (i.e. thread-local) transitions and global operations. Then, every interleaving is explored among these transitions when calculating abstract successor states. Note that these solutions employ a crude version of POR, with no dynamic element.

VVT [27] uses an LLVM-based front-end to verify C programs, which determines blocks of instructions that can execute atomically without interfering with the allowed set of outcomes. Then, these blocks serve as the individual transitions in a large-block encoded CEGAR loop.

In comparison, CPAchecker [11] uses a pre-processing step on the edges of the CFAs to determine thread-local and global operations, then uses a similar large-block encoded CE-GAR loop. In addition, it uses several further optimization steps to be more performant; such as *waitlist ordering* and *partitioning of abstract states*.

### 3.2 Weakly Ordered Concurrency

The algorithm presented in this report has been heavily influenced by three existing tools, namely, HERD [7], DARTAGNAN [21] and RCMC [32]. In this section, I will present the approaches employed by these tools.

$<sup>^{1}</sup>$ At the time of writing this report, I have no knowledge of any approach that utilizes any form of abstract reasoning over declarative semantics.

Figure 3.1: HERD's input litmus test and the generated candidate executions

#### 3.2.1 Herd

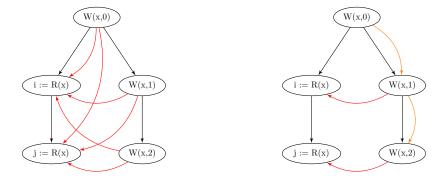

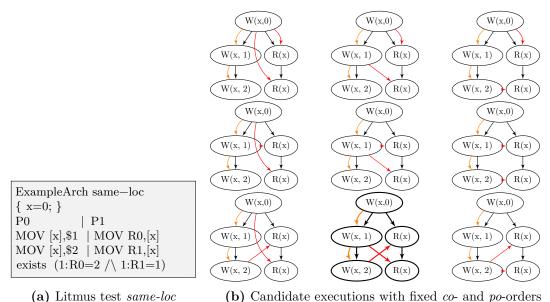

HERD is a memory model simulator [7]. It expects a memory model specification written in the CAT language [8] and a litmus test. Litmus tests are small, assembly-level concurrent programs that include accesses to global memory, as well as constraints on local variables. Litmus tests are widely used to specify guarantees of memory models, e.g. Intel most notably only uses such programs as the specification of the X86 memory model [17]. For example, a memory model rule might forbid the reordering of same-location accesses. The corresponding litmus test in Figure 3.1a has two threads: a producer with two consecutive *Write* events, and a consumer with two consecutive *Read* events, all to the same location. Any execution is forbidden where the consumer observes the two written values in reverse order, i.e. the value of R1 is 1 from the earlier *Write*, while the value of R0 is 2 from the second *Write*. This outcome is only possible when either the *Reads* or the *Writes* have been reordered.

For a given memory model and litmus test, the question is whether the forbidden behavior is *observable* on the target architecture. To answer this question, HERD will first generate all candidate executions of the litmus test. This is done in an enumerative way: for each primitive relation every semantically correct combination will be explored [7], as seen in Figure 3.1b. After enumeration, the candidate executions are filtered based on whether they are consistent with the specified memory model. If any consistent execution graph of the litmus test produces the forbidden outcome, the specified behavior is *observable* and the litmus test fails. For the example in Figure 3.1a, there is one such candidate execution (given fixed *co-* and *po-*orders), highlighted in bold in Figure 3.1b.

The example in Figure 3.1 also shows that the number of *candidate executions* is generally much higher than the number of *consistent execution graphs*. Given a memory model rule that forbids the reordering of same-location accesses, only 6 *candidate executions* are *consistent* out of the 9 in Figure 3.1b given the fixed *co*-order. However, the total number of *candidate executions* are much higher. The *Write* events can be ordered by any of their permutations, as the algorithm cannot assume that any of those partial orders is inconsistent without taking the memory model into account. However, given the forbidden

Figure 3.4: Execution graphs generated by RCMC

same-location reordering, only the one in Figure 3.1b is consistent with the memory model. This puts the number of all candidate executions at 3! \* 9 = 54, and the percentage of consistent execution graphs at 11.1%. For larger programs, this ratio is even smaller, as the number of unnecessary partial orders becomes higher. This observation is also established by the practical evaluation of the RCMC tool, which only generates consistent execution graphs [32].

The goal of HERD is not general program verification, but rather architectural verification. Litmus tests are by definition small programs, and therefore it is unnecessary to optimize the algorithm in HERD for input size. For anything larger than an ordinary litmus test, HERD will most likely time out while enumerating the candidate executions. This prompted the development of smarter *candidate execution* generation, such as RCMC [32].

#### 3.2.2 Rcmc

The novelty of RCMC is its smart exploration algorithm. In each step of its algorithm, RCMC will only generate consistent execution graphs, and no execution graph is ever explored twice. The implemented *stateless* model checking algorithm receives a concurrent C/C++ program with optional assertions, and enumerates all consistent executions as its output. If in any of the execution graphs the assertion is violated, or a non-atomic concurrent

access occurs, the tool reports the program as *unsafe* immediately. Note that the memory model is *not* an input, as the C/C++ concurrency model (as formalized in the repaired RC11 memory model [34]) is hard-coded into the algorithm. This significantly reduces the applicability of the tool for custom architectures and potentially yields false positive results.

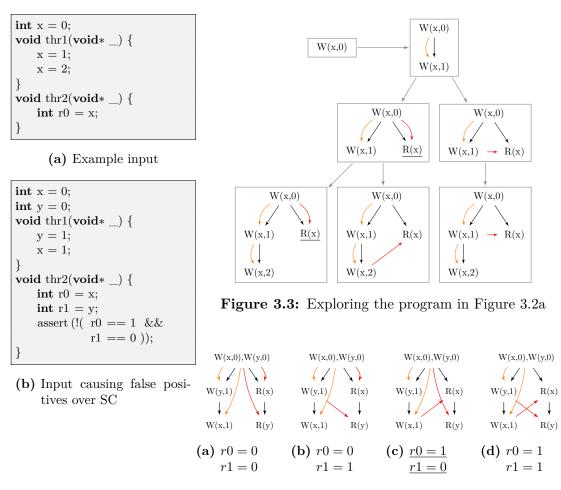

Consider the input program in Figure 3.2a. Two threads are executing concurrently, one writing to memory and another reading from it. Note that atomic accesses have been replaced with regular assignments for the sake of brevity. For the sake of this example, *relaxed* accesses can be assumed.

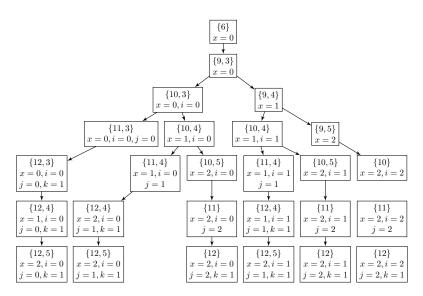

The execution of the algorithm can be seen in Figure 3.3. RCMC will start by recording the initial values in a node, then one-by-one adding the statements of the program. Any time a *Read* event is added, each subexecution is explored where *Read* receives a value from any existing *Write* event. In exactly one of the subexecutions, *Read* remains *revisitable*, i.e. a later *Write* can provide it a value. *Revisitable* nodes are underlined in the example. Each time a *Write* event is added, each subexecution is explored where the newly added *Write* provides a value for any combination of currently *revisitable Reads*. Furthermore, each consistent *co*-order is also explored, but in Figure 3.3, this is deterministic due to *po*. In the example in Figure 3.3, the order of recorded nodes alternates between the two threads, starting with a *Write* event to *x*.

The novelty behind the algorithm is to use *revisitable* nodes to mark a single subexecution where a given *Read* event's value is not final. If more than one such subexecution existed, adding a subsequent *Write* event could generate redundant subexplorations [32].

Consider the input program in Figure 3.2b and the generated execution graphs in Figure 3.4. Depending on the received values in the second thread, an assertion failure can occur. The condition of the assertion means that the second *Write* event executed *before* the previous one. This is observable in Figure 3.4c. Considering C/C++ can generally run on any architecture, one cannot assume that the hardware is not e.g. sequentially consistent (SC). SC guarantees that no statements will be reordered, and therefore the assertion is never violated. RCMC, however, reports it as unsafe because C/C++ does not guarantee this assumption, and therefore this can be categorized as a false positive result. This is not a shortcoming of the algorithm itself, but rather of the approach: one cannot assume that the memory model of a programming language is independent of the target architecture [41]. Such a false result might shadow actual problems in the input program, and is therefore inherently unsafe.

Another problem of RCMC is the suboptimal exploration of executions when multiple threads write the same variable. As noted above, exploring artificially generated *co*-orders is detrimental to the number of execution graphs. In the worst case, each new *Write* event will effectively multiply the number of subexecutions by the factor of existing *Write* events to the same variable, even if only one thread observes the value. In this case, enumerating all execution graphs where this *Read* reads from a different *Write* would suffice, yet this is multiplied by the factorial of the number of *Write* events, as seen in Figures 2.7d and 2.7e.

#### 3.2.2.1 GenMC

As an imprevement to RCMC, GENMC [33] promises to deliver a memory model-aware, stateless model checking algorithm. This enables the verification of software running on custom memory models with an approach very close to that of RCMC. However, the boundedness of the algorithm is still a considerable drawback (as it is with RCMC as well).

|           |              |              |              | Optimal     | Handle       |

|-----------|--------------|--------------|--------------|-------------|--------------|

|           | Software     | Parametric   |              | execution   | unbounded    |

|           | verification | memory model | Scalable     | enumeration | state spaces |

| Herd      | ×            | $\checkmark$ | X            | ×           | X            |

| RCMC      | 1            | ×            | $\checkmark$ | ✓*          | ×            |

| Dartagnan | 1            | $\checkmark$ | $\checkmark$ | N/A         | ×            |

Figure 3.5: Comparison of related verification tools

#### 3.2.3 Dartagnan

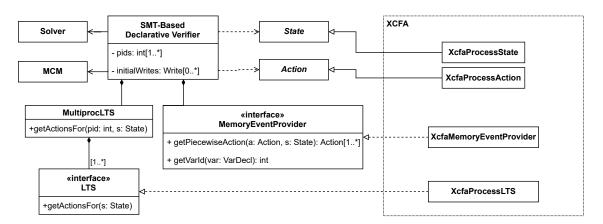

Most of the concerns above are addressed by DARTAGNAN, a bounded model checker that uses memory models as modules [21, 25]. DARTAGNAN expects a concurrent program and a memory model as inputs, and using the conjunction of SMT-encoded expressions determines whether an unsafe state is reachable within a given bound. To achieve this, DARTAGNAN unrolls and encodes the concurrent program as an SMT-expression; encodes the unsafe state as another SMT-expression; and encodes the input memory model as an SMT-expression. If the conjunction of the expressions above is *satisfiable*, the unsafe state is *reachable* and therefore the concurrent program is *unsafe*.

DARTAGNAN is a software verification tool, complete with an integration to SMACK [37], an LLVM-based program transformation tool that allows DARTAGNAN to work on formal models rather than source-level programs. The gap between the higher-level LLVM-IR and the ISA of the target architecture is bridged by using *compiler mappings* for translating e.g. memory ordering primitives [21]. This is a conventional procedure [41], but special attention has to be paid to ensure the compiler mappings represent an actual compiler's behavior that might be used to compile the examined program later on.

In comparison with HERD and RCMC, DARTAGNAN (and its companion tool, PORTHOS [21]) is not capable of enumerating consistent executions. Even though as a reachability checker, DARTAGNAN is not expected to provide this feature, it could be useful to provide a way to use the tools embedded into other verification algorithms for handling concurrent parts of an otherwise independent set of threads. In this case, an unsafe state might not only be dependent on the concurrent parts of the program, and therefore DARTAGNAN could not handle it on its own.

Evaluating the five criteria in Figure 3.5 reveals that none of the tools fulfil every aspect. HERD is not capable of software verification due to scaling issues caused by its suboptimal execution enumeration approach. RCMC is not parametric and therefore only C/C++ guarantees are assumed, and it uses artificially generated *co*-orders which increase the number of explored execution graphs. DARTAGNAN cannot enumerate consistent execution graphs. Furthermore, neither solution can handle unbounded programs.

## Chapter 4

# SMT-Based Verification over Declarative Semantics

In most memory model-aware verification tools (such as HERD [7] and RCMC [32]), the consistent candidate executions are create *generatively*, i.e., by starting from an empty execution and adding events and locations until a complete candidate execution is created. If reachability of some error state is required, their approach is to enumerate all consistent executions, and see whether any include the given state. In contrast, SMT-based verification tools such as DARTAGNAN use an SMT-solver instead, and encode the unsafe state explicitly in the query. While this introduces the complexity of dealing with an SMT-solver, the acquired benefit of answering reachability queries directly make it worthwile.

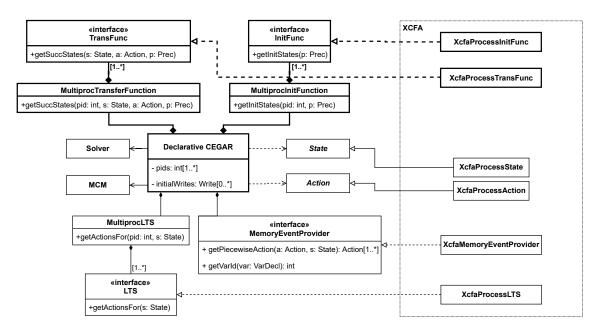

In this chapter, I introduce my implementation of an SMT-based algorithm for verifying reachability over declarative semantics, influenced greatly by DARTAGNAN. Throughout this chapter, all my work can be assumed to have taken place in THETA [40], a configurable and modular verification framework I am a developer of<sup>1</sup>. However, the implementation is subject to change in the future, and therefore I do not consider it an artifact of this thesis.

### 4.1 Representing the Input Program

THETA includes support for a diverse set of input formalisms, such as Extended Timed Automata (XTA), Symbolic Transition Systems (STS) and Control Flow Automata (CFA) [28]. While all of these have roughly the same expressive power, they lack certain features that make it hard to represent parallelism. Most notably, none of these provide any information on the structural composition of the source model. Therefore, I opted to implement and use a version of the previously introduced eXtended Control Flow Automata (XCFA) formalism. In this section, I introduce this implementation an elaborate on its features.

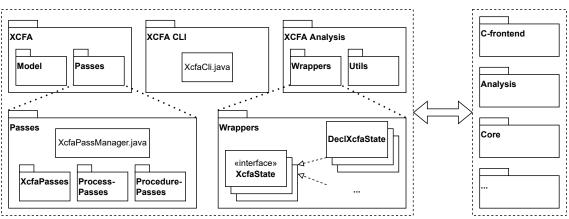

THETA achieves its modularity by clearly abstracting formalism-specific parts of the verification algorithms away from the core analysis modules [22, 28]. Furthermore, for each formalism, the code is divided into three main packages:

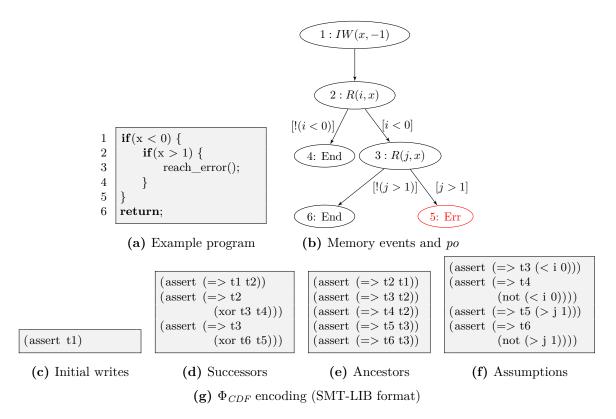

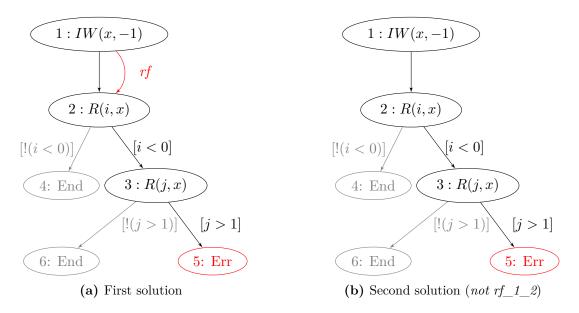

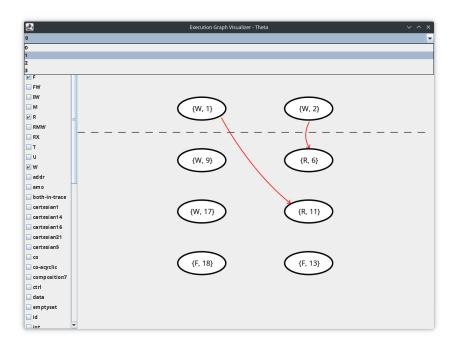

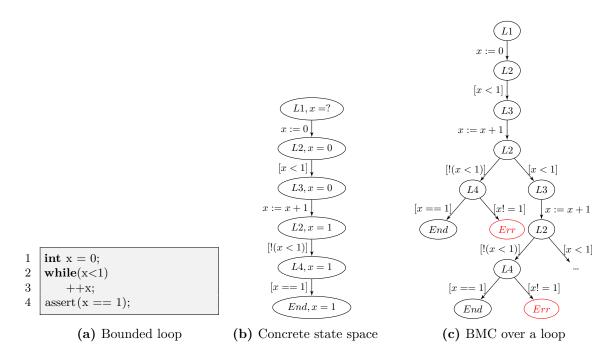

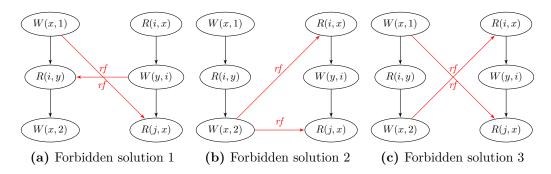

• the core formalism, containing the classes used for the in-memory representation of the model;