**Budapest University of Technology and Economics** Faculty of Electrical Engineering and Informatics Department of Measurement and Information Systems

# Stateless software model checking parameterized with memory consistency models

BACHELOR'S THESIS

Author Levente Bajczi Advisor Dr. Vince Molnár

December 11, 2020

# SZAKDOLGOZAT FELADAT

# Bajczi Levente

Mérnökinformatikus hallgató részére

# Memóriamodellekkel paraméterezhető állapotmentes szoftver-modellellenőrzés

A kritikus beágyazott rendszerek világában mind a mai napig nem terjedtek el igazán amodern, többmagos, párhuzamos programok hatékony futtatására képes processzorok. Ennek egyik oka, hogy a több magon futó párhuzamos programok helyességének ellenőrzése nagyon nehéz feladat – a legtöbb hibát teszteléssel közel lehetetlen felderíteni, a formális ellenőrző algritmusok fejlettsége pedig csak mostanában kezdi elérni azt a szintet, ahol a probléma megoldhatóvá válik.

A többmagos rendszerek komplexitásának egy nagy részét a magok által közösen használt memória elérését szabályozó bonyolult memóriamodellek adják. Ezek bizonyos esetekben lehetővé teszik, hogy egyes memóriaműveleteket a hatékonyság érdekében átsorrendezzünk – ez viszont a megszokott, szekvenciális végrehajtáshoz képest új, szokatlan viselkedésekhez vezethet. Amellett, hogy ez a fejlesztők számára is nehézséget jelent, a legtöbb formális ellenőrző eszköz sincs felkészítve a szekvenciálistól eltérő memóriamodellek kezelésére. Fontos lenne tehát egy olyan ellenőrző algoritmus kifejlesztése, amely *paraméterezhető* az architektúra által használt memóriamodellel.

A hallgató feladatának a következőkre kell kiterjednie:

- Mutassa be a párhuzamos programok ellenőrzésére használható létező algoritmusokat, különös tekintettel a szekvenciálisnál gyengébb memóriamodelleket is támogató megoldásokra.

- Egy jelenleg korszerűnek számító megoldásra építve vizsgálja meg, hogyan lehetne azt kiterjeszteni úgy, hogy a memóriamodell az algoritmus számára bemenetként szolgáljon.

- Implementálja a választott algoritmust, és tegyen kísérletet a javasolt kiegészítések megvalósítására is.

- Tesztekkel és mérésekkel vizsgálja meg a javasolt kiterjesztések helyességét és teljesítményét az eredeti algoritmushoz képest.

Tanszéki konzulens: Dr. Molnár Vince, adjunktus

Budapest, 2020.10.11.

.....

Dr. Dabóczi Tamás tanszékvezető egyetemi tanár, DSc

# HALLGATÓI NYILATKOZAT

Alulírott *Bajczi Levente*, szigorló hallgató kijelentem, hogy ezt a szakdolgozatot meg nem engedett segítség nélkül, saját magam készítettem, csak a megadott forrásokat (szakirodalom, eszközök stb.) használtam fel. Minden olyan részt, melyet szó szerint, vagy azonos értelemben, de átfogalmazva más forrásból átvettem, egyértelműen, a forrás megadásával megjelöltem.

Hozzájárulok, hogy a jelen munkám alapadatait (szerző(k), cím, angol és magyar nyelvű tartalmi kivonat, készítés éve, konzulens(ek) neve) a BME VIK nyilvánosan hozzáférhető elektronikus formában, a munka teljes szövegét pedig az egyetem belső hálózatán keresztül (vagy autentikált felhasználók számára) közzétegye. Kijelentem, hogy a benyújtott munka és annak elektronikus verziója megegyezik. Dékáni engedéllyel titkosított diplomatervek esetén a dolgozat szövege csak 3 év eltelte után válik hozzáférhetővé.

Budapest, 2020. december 11.

Bajczi Levente hallgató

# Contents

| Kivonat  |                |         |                                     |      |  |  |  |  |

|----------|----------------|---------|-------------------------------------|------|--|--|--|--|

| Abstract |                |         |                                     |      |  |  |  |  |

| 1        | Intr           | roducti | ion                                 | 1    |  |  |  |  |

| <b>2</b> | Background     |         |                                     |      |  |  |  |  |

|          | 2.1            | Concu   | rrent Software                      | . 3  |  |  |  |  |

|          | 2.2            | Multi-  | Core Hardware                       | . 4  |  |  |  |  |

|          |                | 2.2.1   | Memory Model                        | . 5  |  |  |  |  |

|          |                |         | 2.2.1.1 Memory Model Specifications | . 8  |  |  |  |  |

|          |                |         | 2.2.1.2 Memory Model Faults         | . 9  |  |  |  |  |

|          | 2.3            | Softwa  | are Verification                    | . 9  |  |  |  |  |

|          |                | 2.3.1   | Model Checking                      | . 9  |  |  |  |  |

| 3        | Related Work 1 |         |                                     |      |  |  |  |  |

|          | 3.1            | Assum   | ning Sequential Consistency         | . 11 |  |  |  |  |

|          | 3.2            | Gettin  | ng Weaker                           | . 12 |  |  |  |  |

|          |                | 3.2.1   | Weakly Ordered Languages            | . 13 |  |  |  |  |

|          |                | 3.2.2   | Weakly Ordered Hardware             | . 13 |  |  |  |  |

|          | 3.3            | Handl   | ing Faults                          | . 14 |  |  |  |  |

| <b>4</b> | Algorithm 16   |         |                                     |      |  |  |  |  |

|          | 4.1            | Execu   | tion Graphs                         | . 16 |  |  |  |  |

|          |                | 4.1.1   | Initial Values                      | . 17 |  |  |  |  |

|          |                | 4.1.2   | Handling a Write                    | . 17 |  |  |  |  |

|          |                | 4.1.3   | Handling a Read                     | . 17 |  |  |  |  |

|          |                | 4.1.4   | Handling Revisit Sets               | . 18 |  |  |  |  |

|          |                | 4.1.5   | Effect of the Memory Model          | . 19 |  |  |  |  |

|          | 4.2            | Genera  | ating the Executions                | . 20 |  |  |  |  |

|              |     | 4.2.1        | Executing a Statement                                                                     | 21 |  |  |  |

|--------------|-----|--------------|-------------------------------------------------------------------------------------------|----|--|--|--|

|              |     |              | 4.2.1.1 NewRead                                                                           | 21 |  |  |  |

|              |     |              | 4.2.1.2 NewWrite                                                                          | 22 |  |  |  |

|              | 4.3 | Is an l      | Execution Legal?                                                                          | 24 |  |  |  |

|              |     | 4.3.1        | Permanence                                                                                | 25 |  |  |  |

|              | 4.4 | Sound        | ness and Optimality                                                                       | 27 |  |  |  |

|              |     | 4.4.1        | Soundness                                                                                 | 27 |  |  |  |

|              |     | 4.4.2        | Optimality                                                                                | 28 |  |  |  |

| 5            | Imp | olemen       | tation                                                                                    | 29 |  |  |  |

|              | 5.1 | The F        | ormalisms                                                                                 | 29 |  |  |  |

|              | 5.2 | The A        | lgorithm                                                                                  | 32 |  |  |  |

| 6            | Eva | Evaluation 3 |                                                                                           |    |  |  |  |

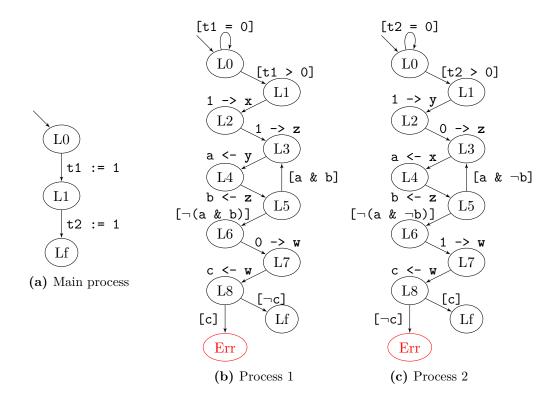

|              | 6.1 | Carryi       | ng Out Hardware-Software Co-Verification Tasks                                            | 35 |  |  |  |

|              |     | 6.1.1        | Memory Modeling                                                                           | 35 |  |  |  |

|              |     |              | 6.1.1.1 Modeling Faulty Hardware                                                          | 37 |  |  |  |

|              |     | 6.1.2        | Mapping Programs to Formal Models                                                         | 37 |  |  |  |

|              |     | 6.1.3        | Verifying Litmus Tests                                                                    | 38 |  |  |  |

|              |     |              | 6.1.3.1 The $2w2r$ Litmus Test                                                            | 39 |  |  |  |

|              |     |              | 6.1.3.2 The $cow2r$ Litmus Test $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 39 |  |  |  |

|              |     |              | 6.1.3.3 The $coww2r2r$ Litmus Test $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$     | 40 |  |  |  |

|              |     |              | 6.1.3.4 The $mp$ Litmus Test                                                              | 40 |  |  |  |

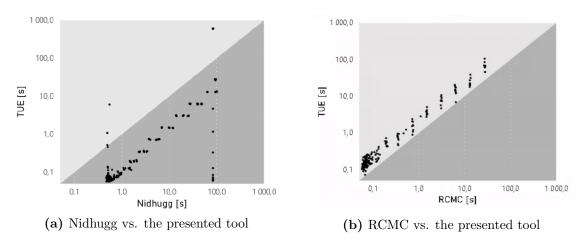

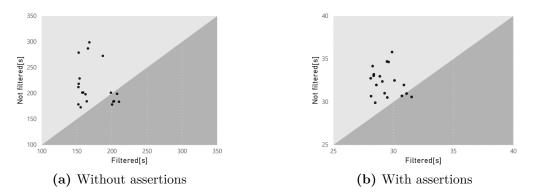

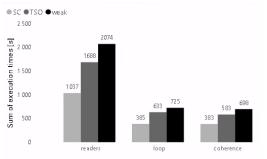

|              | 6.2 | Perfor       | mance Evaluation                                                                          | 41 |  |  |  |

|              |     | 6.2.1        | Performance Evaluation Details                                                            | 42 |  |  |  |

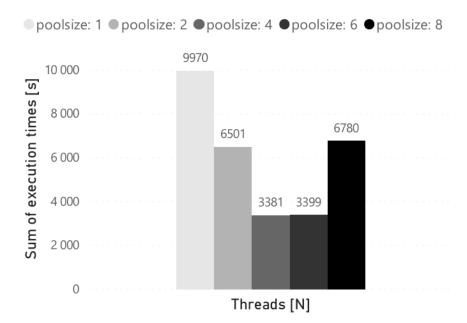

|              | 6.3 | Scalab       | ility Dimensions                                                                          | 46 |  |  |  |

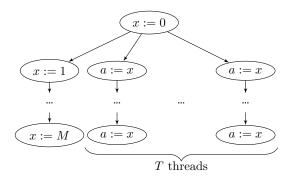

|              |     | 6.3.1        | The Test Program                                                                          | 46 |  |  |  |

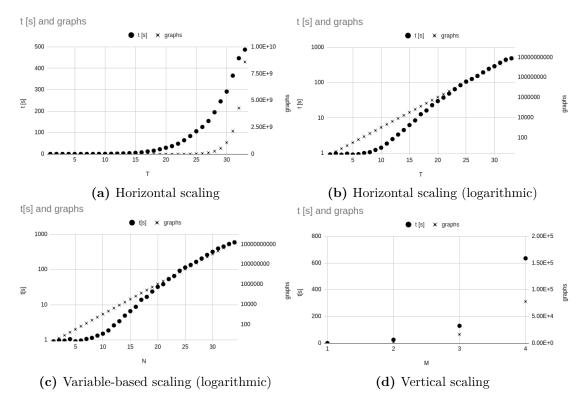

|              |     | 6.3.2        | Horizontal Scaling                                                                        | 46 |  |  |  |

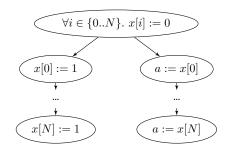

|              |     | 6.3.3        | Variable-Based Scaling                                                                    | 47 |  |  |  |

|              |     | 6.3.4        | Vertical Scaling                                                                          | 47 |  |  |  |

|              |     | 6.3.5        | Redundancy of the <i>mo</i> -Order                                                        | 48 |  |  |  |

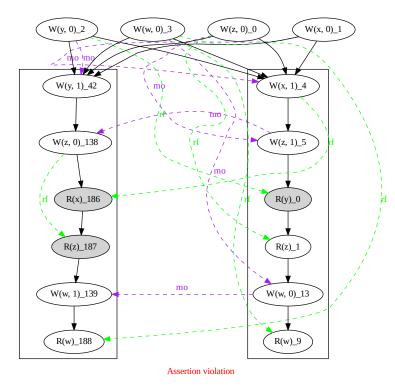

|              | 6.4 | Case S       | Study                                                                                     | 48 |  |  |  |

|              | 6.5 | Future       | e Work                                                                                    | 51 |  |  |  |

| Bibliography |     |              |                                                                                           |    |  |  |  |

| $\mathbf{A}$ | MC  | M Ma         | pping Among Formalisms                                                                    | 55 |  |  |  |

# Kivonat

A többmagos hardveren futó többszálú programok formális verifikációja sokáig a terület legnagyobb kihívásai közé tartozott. A probléma nehézségét elsősorban a szálak végrehajtásainak tetszőleges átfedése jelenti. Ennek ellenére a többmagos beágyazott processzorok iránti igény egyre hangsúlyosabban megjelenik biztonságkritikus környezetben is, elkerülhetetlenné téve, hogy a problémakörrel foglalkozzunk. A többszálú programok nemdeterminisztikus viselkedése ugyanis nagyban megnehezíti a tesztelésüket, így még fontosabbá válik a formális módszerek használata.

Ezen felül a többmagos processzorok a teljesítmény növelése érdekében sok optimalizációs technikát tartalmaznak – egy ilyen módszer a memóriakezelő utasítások átrendezésének lehetővé tétele. Ennek motivációja az, hogy a processzor az általánosan sokkal lassabb memóriautasítások befejezésére való várakozás közben is hasznos munkát végezhessen. Az átrendezés azonban bizonyos esetekben váratlan viselkedésekhez vezethet a tisztán szekvenciális futáshoz képest. Kevés ellenőrzési módszert adaptáltak ezen viselkedés kezelésére, és ezek többsége is előre meghatározott memóriamodelleket feltételez, melyek testreszabása nem lehetséges. Ez csökkenti a módszerek alkalmazhatóságát, mivel a legtöbb hardver nem teljesen feleltethető meg egy-egy elméleti modellnek (akár szándékosan, akár tervezési hibák miatt).

Ezen dolgozatban egy olyan algoritmust mutatok be, ami bemenetként egy futásidejű hibadetektálásokkal (assert) annotált programot és egy memóriamodellt fogad, kimenetként pedig megadja, hogy az adott memóriamodellt betartó processzoron futtatva elérhető-e hibaállapot a programon belül. Az algoritmus az *állapotmentes modellellenőrzés* megközelítésére épít, és okos állapottér-bejárási stratégiájával lényegesen kisebb memóriahasználatot eredményezhet, mint a hagyományos modellellenőrző algoritmusok. A dolgozatban belátom, hogy – bizonyos feltételeknek megfelelő programok esetén – az algoritmus helyes, és optimális a megvizsgált lefutások tekintetében. Ezen felül néhány ismert architektúrára és programra alkalmazva a teljesítményét is kiértékelem, korszerű szoftvermodellellenőrző eszközökkel összehasonlításban. Munkám eredménye várhatóan hozzájárul majd a többmagos architektúrákon futó többszálú szoftverek kritikus beágyazott rendszerekben való elterjedéséhez, ezzel végső soron jobb teljesítményt és alacsonyabb költségeket hozva az érintett iparágakban.

A dolgozatban ismertetett eredmények a Budapesti Műszaki és Gazdaságtudományi Egyetem Villamosmérnöki és Informatikai Kar Balatonfüredi Hallgatói Kutatócsoport szakmai közössége keretében jöttek létre a régió gazdasági fejlődésének elősegítése érdekében. Az eredmények létrehozása során figyelembe vettük a balatonfüredi központú Rendszertudományi Innovációs Klaszter által megfogalmazott célkitűzéseket, valamint a párhuzamosan megvalósuló EFOP 4.2.1-16-2017-00021 pályázat támogatásával elnyert "BME Balatonfüredi Tudáscentrum" térségfejlesztési terveit.

Az Innovációs és Technológiai Minisztérium ÚNKP-20-1 kódszámú Új Nemzeti Kiválóság Programjának a Nemzeti Kutatási, Fejlesztési és Innovációs Alapból finanszírozott szakmai támogatásával készült.

# Abstract

Formal verification of multithreaded software running on multi-core hardware has for long been challenging for anything other than the simplest of programs. The complexity of dealing with the arbitrary interleavings of such a program makes it one of the hardest problems of software verification. However, the industry trend of introducing embedded multi-core processors into the world of safety critical systems makes it unavoidable having to deal with this problem, because formal methods are even more important for concurrent programs due to their inherent nondeterminism, which makes testing unreliable.

Furthermore, multi-core processors offer many types of optimizations to decrease execution time – one such technique is to allow the reordering of memory accesses whenever possible, to avoid having to wait for the typically much slower memory instructions to finish. This may introduce unexpected behavior compared to a purely sequential execution. Few analyses have been adapted to deal with such behavior, and most of them follow predefined memory models hard-coded into their algorithms without providing any facilities to customize it. This hurts the applicability of such techniques, as most types of hardware do not fully conform to theoretical models (either by design, or due to design flaws).

In this work I propose an algorithm that accepts a concurrent program including assertions and a memory model as inputs, and reports whether the program can reach an erroneous state when run on a processor that abides by the given memory model. This algorithm builds on the *stateless model checking* approach, which yields a significantly lower memory usage than other techniques by using a smart exploration strategy to manage the large state space. I show that the algorithm is optimal in terms of explored executions and sound when the program meets certain criteria. Furthermore, I apply the algorithm to several well-known architectures and programs, and evaluate its performance compared to state-of-the-art software model checking tools. The expected impact of this work is to facilitate the correct implementation of concurrent software on multi-core architectures, ultimately leading to better performance and lower costs in embedded systems.

The results presented in this work were established in the framework of the professional community of Balatonfüred Student Research Group of BME-VIK to promote the economic development of the region. During the development of the achievements, we took into consideration the goals set by the Balatonfüred System Science Innovation Cluster and the plans of the "BME Balatonfüred Knowledge Center", supported by EFOP 4.2.1-16-2017-00021.

Supported by the ÚNKP-20-1 New National Excellence Program of the Ministry for Innovation and Technology from the Source of the National Research, Development and Innovation Fund.

# Chapter 1

# Introduction

Safety critical embedded systems surround us in most aspects of our lives. The software in cars, elevators, airplanes and power plants are expected to virtually  $never^1$  fail – a metric not easily achievable through conventional testing methods. Thus, a more rigorous approach is necessary for reasoning about the correctness of software systems: formal software verification.

Formal verification aims to prove correctness (e.g. all safety requirements are respected) in a mathematically precise way [18]. This process is generally very resource intensive, and therefore only the most critical components have been traditionally verified using this approach. However, even such components have been getting more and more complex, necessitating the rapid development of verification techniques.

One phenomenon behind this trend of increasing complexity is the use of multi-core processors in embedded systems to run concurrent programs, which is partly caused by the industry approaching the upper limits of single-core performance yet needing more [31], and partly due to cost saving measures – in modern processor manufacturing processes, a lower clocked but multi-core CPU is often cheaper than a single-core but more powerful one.

However, concurrent semantics allow arbitrary interleaving among the threads of a program, often making its state space of possible behaviors undepictably large. This represents a barrier for verification tools that employ any kind of state enumeration technique, and therefore new methodologies are required to deal with this problem.

To combat the obstacle of state enumeration, several specialized approaches have been developed that aim to decrease the number of executions to be explored – one of the first such algorithms for concurrent programs is *Partial Order Reduction* (POR) [34], which determines whether some executions are equivalent on some abstraction level in their outcomes, and then explores only a representative trace. However, this method also records all explored executions (to determine whether a new candidate execution is equivalent to an already handled one), meaning the memory usage tends to scale poorly.

In conventional software verification, to avoid having to keep a record of each state (and therefore to decrease the memory usage), one might use a *stateless* model checking algorithm. This family of algorithms explore all reachable states of the program without recording them. However, special techniques must be employed to distinguish the reach-

$<sup>^1\</sup>mathrm{For}$  example, a SIL 4-classified component is expected not to fail until more than 10 000 years of continuous use

able states based on their equivalence – this has led to algorithms such as *Dynamic Partial* Order Reduction (DPOR) [19].

Furthermore, even if an algorithm can handle concurrent program semantics, there are many aspects to dealing with *multi-core* processors and real concurrency, as opposed to single-cores and apparent concurrency (parallelism). One of these aspects is the *weakened* memory model of such CPUs, which allows the reordering of memory accesses whenever possible, in order to avoid having to wait for the typically much slower memory instructions to finish [20]. However, this introduces unexpected behavior when only *sequential* semantics is taken into account, either by a programmer developing software for multi-core hardware, or by *verification tools themselves*.

However, even if a specific algorithm can handle the *weak* semantics of a given hardwaresoftware co-verification problem, it might still occur that an assumption of the tool does not hold. One such example is the verification of flawed memory architectures, where the design does not follow a predefined template for weak memory – such as the ARM Cortex A9 processor that includes a fault where same-variable reads can be reordered, which goes against the specifications of the ISA [1]. In this case, any tool using standard memory models might fail to report safety violations, thus a *parameterizable* solution is necessary, which can handle any memory model.

At the time of submitting this work, no real solution exists to this problem. I presented this problem in my earlier  $TDK^2$  submission in 2018 [9], where I provided a hardwarecentric approach as the solution, which used litmus tests as test cases and conventional model checking algorithms as a reasoning tool, which was however limited by the utilized tools' capabilities. In the paper presented at the *EMSOFT19* conference [10], we have defined the scope of the problem and formalized the problem statement, as well as provided a theoretical solution to the problem. In this work, I propose a *stateless model checking algorithm parameterized with memory consistency models*, which satisfies the criteria imposed by the problem statement. Furthermore, I implement the novel algorithm in the Theta verification framework [32] to show its applicability and scalability compared to similar, but not entirely adaptable model checking tools.

This work is structured as follows: After presenting the theoretical background of the ideas behind the solution (Chapter 2), I introduce the model checking algorithms and tools that are closest in the targeted use-case of the problem above (Chapter 3). Afterwards, I present the proposed algorithm through examples and formal specification (Chapter 4), as well as elaborate on its implementation aspects (Chapter 5). Finally, I evaluate the functional, usability and performance properties of the created tool (Chapter 6).

<sup>&</sup>lt;sup>2</sup>Students' Scientific Conference/Tudományos Diákköri Konferencia (hu)

# Chapter 2

# Background

In this chapter I introduce the core concepts of the concurrent software model checking field. Firstly, I establish the basis of the *concurrent software* paradigm I aim to analyze, after which I show the properties of the *multi-core hardware* they can be run on. Finally, I present the foundations of *software verification*, the approach to reason about the correctness of a software product.

# 2.1 Concurrent Software

At the beginning of the history of digital computing – due to the single processing units of the era's CPUs – software was running sequentially, executing the instructions in the order it was specified in its source. The current state of the program could be given with the *current stack s and the valuation of the variables in the global memory v*. When the first multitasking operating systems appeared, these programs moved into *processes* and *threads*<sup>1</sup> (see Definition 2.1.1), but were still only executing on a single processing unit and therefore were still sequential, even though multiple processes could overlap during their execution, providing a false sense of parallelity. This *apparent concurrency* paired with sequentially ordered processes and threads had been the *programmer's view* for quite a few decades before the first devices capable of *real concurrency* [13] arrived to the general consumer. Up until then, actual parallelity was mostly a niche subject of distributed systems [14], and had not reached the mainstream software developer's world – and even if it did, the sequentiality property was never violated.

#### Definition 2.1.1: Concurrent programs

A concurrent program is a program containing more than one thread executing in parallel. In this work, it is assumed that a concurrent program p(T, Q) is characterized with the following properties:

- 1. T: The set of threads in p

- 2. Q: The globally accessible variables of p

Note that a program has a predetermined amount of threads.

<sup>&</sup>lt;sup>1</sup>For the sake of simplicity, I use the terms *process* and *thread* interchangeably

However, even in the case of *apparent concurrency*, the number of ways a program with more than a single thread can be executed explodes compared to the only possible execution of a single-threaded program. This is due to the arbitrary interleaving of threads in a system – there are no built-in guarantees concerning the order of execution among them. This also means that the state vector of the program grows, as it is no longer enough to specify the (s, v) tuple – that is valid only for a given thread. The global state can be described with the state vector shown in Definition 2.1.2.

#### Definition 2.1.2: State vector of a concurrent program

The current execution state of a concurrent program p(T, Q) can be described with the following tuple: (S, V, E), where

- 1.  $S \in (s,v)^{|T|}:$  Stacks and valuations of local variables of the individual threads in T

- 2. V: Valuation of global variables Q

- 3. E: Enabled threads in T (i.e. not blocked)

A stack entry contains the following types of information:

- The current location of the execution in the program (like the Program Counter in the hardware)

- The locations to jump back to when a function finishes execution

With the introduction of multi-core processors, the performance limit of a single thread could be overcome by utilizing more processing units. The same multitasking operating systems could be used as before, but with an actual performance benefit to using more threads. However, this also introduced unexpected behavior to programs accessing globally shared memory due to the more advanced memory models of such hardware – the reason for this elevated complexity is explained in detail in Section 4.1.5.

### 2.2 Multi-Core Hardware

As we are approaching the theoretical limits of the maximum frequency in the current technology's processors [31], it has become evident that we need to concentrate on aspects of the microprocessors other than its single-core performance – such as the number of cores it contains, and their effective cooperation. Theoretically, we can almost double the available performance if we double the number of cores, as they can all work in parallel.

The term *multi-core* can mean that a processor either

- has more cores of the same kind (homogenous multi-processing), or

- has more cores of different kinds (heterogeneous multi-processing) [23].

Furthermore, *multi-cores* might differ in terms of access to caches and main memory, how they are interconnected and what isolation is in place among them, if any. A common property of such systems is that they are on a single chip, i.e. the cores reside on the same silicon wafer. Furthermore, legal restrictions have been placed to ensure that the consumer understands the use of the term *multi-core*: the processor manufacturer company AMD

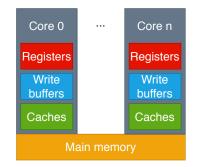

Figure 2.1: Multi-core architecture structure

had erroneously called one of its products an 8-core multicore, when in fact it only had 4 fully-fledged cores, the other 4 being only integer execution  $cores^2$ .

To summarize, the term *multi-core processor* can be used in a lot of ways. In the scope of this work, it is assumed to conform to Definition 2.2.1 and a visualization can be seen in Figure 2.1. However, adhering to its criteria is not easily achievable – for example, the cores cannot communicate among each other, but there still needs to be a total ordering of the memory instructions, as only a single core can assume access to the memory at any time. This arbitration is the task of the *memory model* [20].

### Definition 2.2.1: Multi-Core Processor

In a *multi-core processor*

- 1. there is a single integrated circuit containing more than one homogenous and equally capable execution core,

- 2. each core has access to its own cache hierarchy and local buffers,

- 3. each core has direct access to the main memory of the system,

- 4. the cores can only synchronize with each other through the main memory,

- 5. only one core can assume access to the main memory at a given time.

### 2.2.1 Memory Model

To solve the problem of allowing only a single core to access the memory at a time, most architectures use a separate memory controller that governs access to the main memory. However, it is far from trivial how a total ordering of memory accesses should be produced – it is the task of the *memory consistency model* (MCM) to establish these rules [20].

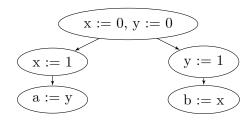

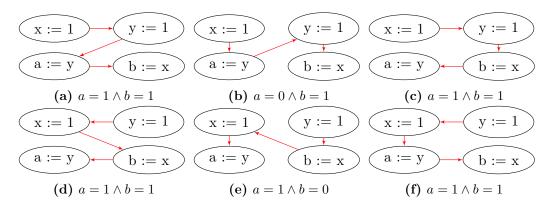

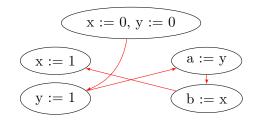

Consider the program containing two threads in Figure 2.2, where each writes to a separate global variable<sup>3</sup> and then prints the other's variable. If we try to sequence these instructions assuming *sequential consistency* (SC, see Definition 2.2.2), we get the 6 possible total orders in Figure 2.4. Note that in no case can *both* read instructions execute before *any* of the write instructions finished – therefore, the outcome  $a = 0 \wedge b = 0$  is not allowed [20].

$<sup>^{2}</sup> https://www.anandtech.com/show/14804/amd-settlement$

<sup>&</sup>lt;sup>3</sup>In all examples the variables  $a, b, c, \dots$  are *local* and  $x, y, z, \dots$  are *global*

Figure 2.2: Two threads performing a global write and read access

Figure 2.3: *a* reads 0 instead of 1

Figure 2.4: Executions of the program in Figure 2.2 assuming SC

During the execution of the program there are four memory accesses: two writes and two reads. These are very expensive in terms of execution time, because generally the main memory is much slower than the processor that accesses it. To lessen the impact of this phenomenon, most modern multi-core architectures employ a *weakened* memory model, meaning that memory instructions do not need to finish<sup>4</sup> before execution can resume [20].

#### Definition 2.2.2: Sequential Consistency (SC)

A sequentially consistent memory model ensures the preservation of all happensbefore relations in the *program order*, i.e. the sequence of instructions in the source. All threads observe the memory in the same way during execution [20].

However, the performance benefit of this *weakened* memory model does not come without a price – it introduces behavior not expected when assuming sequential consistency. If we allow *any* reordering of instructions, the program in Figure 2.2 can have **24** executions in total (any permutation of the four instructions). This could also mean that if a single thread wrote a variable and then read it back, it could be the old value (before the write), as seen in Figure 2.3. The responsibility of any MCM is to constrain the reordering of instructions, to find a balance between performance and unexpected behavior.

An example of a widely used memory model is the *total store ordering* (TSO, see Definition 2.2.3). This is used (among others) in the x86 and x86\_64 architectures, and introduces only a few types of unexpected executions – for example, in the case of the example in Figure 2.2, the previously forbidden outcome  $a = 0 \land b = 0$  is observable, as it is possible that neither of the write operations actually finished before both of the

<sup>&</sup>lt;sup>4</sup>In this context, *to finish* means that the written value has propagated to the global memory and visible by all threads, and a read value is fixed in its target local variable [20]

read accesses returned their values – on any of the threads, they were accessing different variables in memory, and therefore could be reordered.

Definition 2.2.3: Total store ordering (TSO)

The *total store ordering* memory model provides the following guarantees:

1. All accesses to the same memory location are totally ordered

2. All write events are totally ordered.

This means that read instructions can be reordered with other read or write instructions, as long they are accessing different parts of the memory [20].

What most architectures aim to achieve is *coherence* [20]. *Coherence means that if there is a certain order to write events appearing in memory, then all observing threads will see these changes in the same order.* Furthermore, it is desired to only allow causal write-to-read events, as reading from a future write is certainly not the intended outcome a programmer could want. With these constraints, the most permissive memory model is called the *weak memory* model (see Definition 2.2.4). This is most famously used in ARM and RISC-V chips.

#### Definition 2.2.4: Weak memory

A weak memory model only provides the following guarantees:

- 1. All accesses to the same memory location are totally ordered

- 2. All reading threads observe the memory changes at the same time

This means that any two memory instructions accessing different parts of the memory can be reordered on a given thread, but their result will be observable by other threads in a single total order [20].

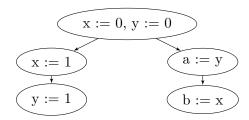

To demonstrate the capabilities of this weakest memory model, take the program in Figure 2.5. There are two threads, one performing two write operations to two distinct memory locations, and the other reads them back in a reverse order. Through intuition (which represents the SC-centric programmer's view), the outcome  $a = 1 \land b = 0$  should be forbidden, because that would mean that by the time the first read returns, the second write has already been finished, but *after that* the first write still has not appeared in memory. However, in the case of weak memory, this is *allowed* in the execution seen in Figure 2.6 – on any of the two threads, the memory operations were accessing different memory locations and therefore could be reordered.

Note, that in the scope of this work, we are talking about the memory models of *hardware*. Concurrent languages such as C/C++ and Java also have memory models, but they serve more as an upper bound on supported relaxation rather than an actually enforceable ruleset. They aim to ensure that one can reason about the possible behavior of portable code as well, where the target platform (and therefore its memory model) is not fixed.

Figure 2.5: Two threads performing two write and two read operations

Figure 2.6: One execution yielding  $a = 1 \wedge b = 0$

### 2.2.1.1 Memory Model Specifications

The formal specification of a memory consistency model describes the actual guarantees a specific architecture provides to the programs running on it. The above mentioned memory models (SC, TSO, weak) are *families* of memory models, and their broadly specified guarantees have to be concretized. In this section, I introduce three ways to provide this specification.

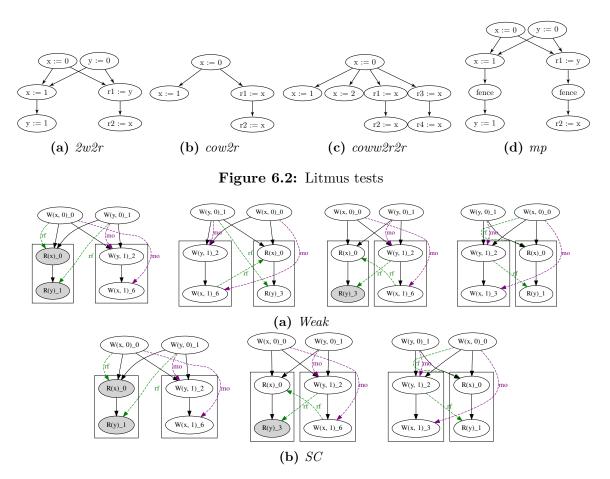

**Litmus tests** Litmus tests are an *example-based* way of providing the specification of the memory model. Litmus tests are small, concurrent programs containing memory accesses and classify outcomes as *forbidden* and *allowed* [20]. This is an *informal* specification, because the set of provided litmus tests can be both incomplete and self-contradicting. However, they provide an easy-to-understand way of communicating the platform specific behaviors to the programmers, and therefore are widely used – Intel for example *only* provides this specification to its memory model [12].

**Microarchitectural specification** The microarchitectural specification describes the exact way a processor solves the memory ordering problem – and therefore it can be classified as the *imperative* specification of a memory model [33]. It contains the pipeline stages of the microprocessor, and the way instructions are treated in each of them. This is harder to grasp for a programmer due to the complexity of the specification, but it is a *formal* specification, and tools can use this to provide insight into the predictable behavior of a program – however, mostly only by *simulating* it, as reasoning about anything bigger than a few lines of code is infeasible through this approach. What it can be used for, however, is to provide a second view into the memory model – for example, verifying if the specified litmus tests of the ISA are honored by the designed architecture.

**Declarative specification** A declarative specification provides certain forbidden patterns over candidate executions [6]. The natural language specification of the memory models above (SC, TSO, weak) are closest to this approach, but the specification is a *formal* rephrasing of the mentioned rulesets. It can be used to validate if a candidate execution is allowed by the architecture, and this approach (in comparison to the microarchitectural specification) is scalable: these patterns are validated on execution graphs, rather than after every instruction. In this work, I am using declarative specifications to verify certain properties of concurrent programs.

#### 2.2.1.2 Memory Model Faults

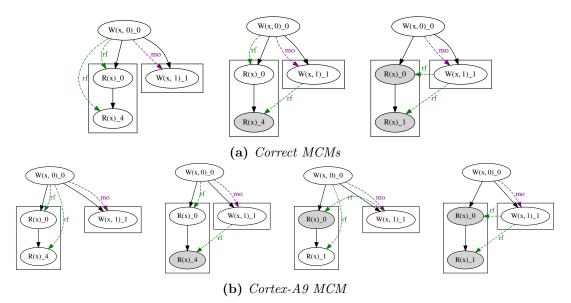

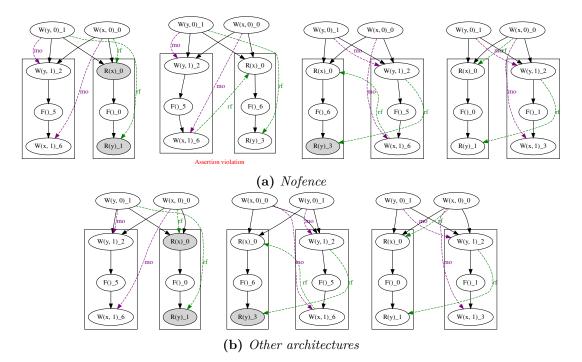

Memory consistency models are complex parts of the architecture, requiring both theoretical planning and corresponding hardware design. This makes it unsurprising that sometimes there are discrepancies between the specification and the actually observable behaviors due to design flaws in the architecture. One such example is the *read-read hazard* found in the ARM Cortex A9 microprocessor [1], which makes it possible that two read instructions accessing the same variable on the same thread are reordered, and therefore observe values in a different sequence than the globally coherent order. Such faults lead to a unique memory model, where not even the most basic assumptions hold [33] – and therefore programs running on them require special procedures to verify their correctness.

# 2.3 Software Verification

Software verification aims to prove that a software product satisfies its requirements [18]. This is done either by testing these properties through running the program on the target platform (called *dynamic verification*), or by analyzing the program with a purpose-built verification tool without having to run it (called *static verification*). The former is useful for catching bugs in the application, but in most cases cannot provide a proof of correctness – there will always be a corner case the testing workflow leaves out. Meanwhile, static verification techniques can perform the following checks (among others) on a software product:

- 1. Anti-pattern detection

- 2. Code conventions verification

- 3. Software metrics calculation

- 4. Formal verification

The first three options are built into most development environments to some extent, and developers use it extensively to receive feedback on the quality of the code before ever running it. The fourth option is more complicated: it aims to verify that formally specified criteria are never violated by a program. This is slowly making its way into the above mentioned IDEs as well, and there are tools that use formal verification techniques to prove common requirements for a broad selection of programs (e.g. all programs written in one programming language)<sup>5</sup>, but the ultimate goal of formal verification is to check project-specific criteria, specified in a formal language. This way, it can be used to possibly provide a *proof of correctness* or a *violation witness* that formally proves or disproves a specified criterion.

### 2.3.1 Model Checking

Model checking is an area of formal verification, which uses a finite-state model of a system (in the case of software verification, a program) for checking whether it meets a given set of criteria, to provide feedback on the product's correctness [17]. It can be used to verify both *liveness* (e.g. the lack of a livelock in the system) and *safety* requirements.

<sup>&</sup>lt;sup>5</sup>For example, *clang-tidy*: https://clang.llvm.org/extra/clang-tidy/

An easy-to-implement approach of model checking is the generation of the state space through enumeration. The state space is the set of all possible states in the model – for example, in the case of a concurrent program, a single state can be described with the state vector in Definition 2.1.2, so the entire state space is the universe over this vector. If we can enumerate all possible states, and can filter out those that are actually reachable, checking the criteria is a simple matter of iterating over this set and proving or disproving the requirements one-by-one. However, it is easy to see that this approach is not feasible for anything other than the simplest of models: if we include a single 32-bit integer in our program, the states required to differentiate its value are  $2^{32}$ . Even if a single state can be stored as simply the value of this integer (so in 4 bytes), the state space would take up more than 17 GB of data. If we included a second integer of the same size, this storage requirement would jump to 147 EB, or  $1.47 * 10^{20}$  bytes, not to mention the time required to iterate over all of these states.

When dealing with concurrent behavior, this already fast growing state space further explodes due to the arbitrary interleavings of the different threads. This leads to the need for a smarter approach for dealing with these kinds of problems. Some of these techniques are introduced in Chapter 3.

# Chapter 3

# **Related Work**

To date, a number of approaches have been developed for dealing with the problem of concurrent software model checking. These techniques are mostly inadequate for verifying criteria on concurrent software models where the system employs a unique memory model. However, these provide the basis for the proposed algorithm for dealing with this problem and thus their introduction is necessary to fully understand the presented approach.

In this chapter I elaborate on some of these techniques, contrasting their targeted use-cases with that of this work.

### 3.1 Assuming Sequential Consistency

When the modeled system provides a sequentially consistent execution environment, the problem simplifies greatly: on any of its threads, the instructions are guaranteed to be executing in the order specified in the source, and their effects are visible to all observing threads at the same time. This means, that the only problem to be tackled is the one introduced in Section 4.1.5 – the large number of the possible states. The standard method of dealing with this problem is to employ a *bounded model checking* algorithm [15, 16] which tries to enumerate all violating states withing a given *bound* of the starting state. To avoid visiting the same state multiple times, this method keeps track of all the states and compares any newly visited state with the elements of this set. This is impractical due to the large memory footprint of this approach, and has lead to another technique called *stateless model checking* [21]. The main premise of this method is that it does not store the set of visited states, but rather uses smart state space exploration techniques to avoid redundant exploration therein.

However, even this smarter technique, when employed naively, is impractical due to the large number of interleavings a program might have among its threads. The original solution to this problem is the *partial order reduction* (POR) algorithm [34], which uses

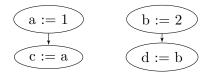

Figure 3.1: All total orders yield  $c = 1 \land d = 2$  because a, b, c, d are thread-local variables, so differentiating among the states is unnecessary

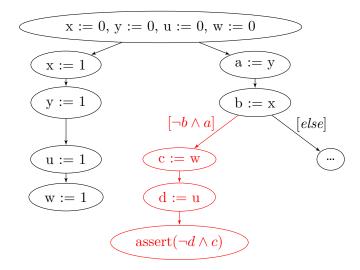

Figure 3.2: The assertion is only reachable when instructions are reordered, and is only violated if other instructions are also reordered

static analyses to discover *thread-local* variables and uses that information to produce a smaller state space, because when a thread only works with local variables, it does not matter whether execution overlaps with another thread doing the same (as seen in Figure 3.1). This approach radically reduced the number of "interesting" states, but was not suitable for large-scale verification due to its reliance on static analyses [19]. To combat this, POR was combined with the idea of *stateless model checking*, resulting in the *dynamic partial order reduction* (DPOR) algorithm [19]. This generated the "interesting" states greedily, when it was time to dissolve a nondeterministic part of the program.

These approaches all assume that the modelled system employs a sequentially consistent memory model, i.e. instructions are never observable out-of-order. As discussed in Section 4.1.5, this is rarely the case due to the aggressive optimization on the processor's part. This means, that while providing stable basis for the following algorithms, they themselves are incapable of handling the proposed problem involving weakly ordered memory.

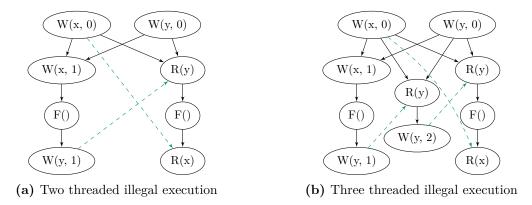

It is important to mention that by itself, this not only means that the SC-assumption is disadvantageous when verifying the requirements, but rather the whole approach is flawed. Take the program in Figure 3.2 as an example: the problem is not only that the body of the assertion never evaluates to *false* over SC ( $w \implies u$  due to program order, and therefore  $\neg d \wedge c$  is always *true*), but also that the location containing the assertion is *not* even reachable with that assumption. This means that even if we replaced the checks with smarter ones that could report such violations, the violating state would never be generated by the underlying algorithm, thus a simple adaptation of these algorithms to weak memory is not enough, new approaches are necessary.

# 3.2 Getting Weaker

When talking about weak memory, it is important to distinguish between memory models of *languages* and *processors*. While there has been substantial work on the modelling of weak memory in processors, most tools that can handle weak memory do so on the abstraction level of the programming language and therefore can assume a rather fixed memory model.

#### 3.2.1 Weakly Ordered Languages

Some algorithms handling weakly ordered languages extend SC algorithms to include previously hidden behaviors in the reachable state space, and some use novel approaches to solve the problem of almost arbitrary reorderings.

An example of the latter is the *CDSChecker* tool [28], which aims to use "several novel techniques for modeling the relaxed behaviors allowed by the memory model and for minimizing the number of execution behaviors" to verify concurrent programs using C/C++ atomics. Even though at the time it performed quite well, compared to other tools of the field, it has since been surpassed in both performance and features by other tools.

An algorithm which extends an SC algorithm to correctly and performantly handle weak memory has only recently been published [24]. This approach (implemented in the tool RCMC) uses a stateless model checking approach, but extends the rules of dissolving nondeterministic read- and write events to correctly handle the weak memory model of the C/C++ language – or rather, the one created by Lahav et al. [26] called RC11, which is the fixed version of the official C11 memory model (in the sense that it is prefix-closed). This algorithm has been the basis for the approach I propose in Chapter 4, but in itself it is not suitable for the verification of systems employing any memory consistency model other than that of RC11 – this means that while a C program might be correct, even taking the weakness of the language into account, the executing hardware might still introduce bugs or constrain the set of observable behaviors yielding false positive and negative proofs.

### 3.2.2 Weakly Ordered Hardware

There had been substantial work in formalizing memory consistency models before [5, 8], but the *cat* language [7] in the tool *herd* [6] revolutionized their specification. Instead of the interleaving semantics, it uses a declarative approach to describe forbidden patterns in the candidate executions of programs and thus constraining the set of executions to that of *observable* executions.

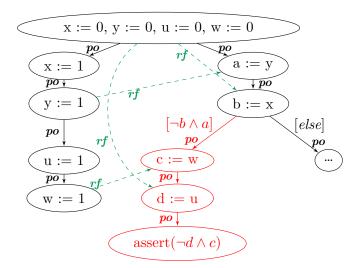

The main idea behind this declarative approach is to keep track of specific relations in the candidate executions, such as:

- po: Relation between immediate successors in the program code

- ppo: Subset of po edges that are respected by the architecture

- *rf*: Read-From relation between a Write and a Read that gets its value from the Write

- fr: From-Read relation between a Read and a Write that gives its value to the Read

Take the program in Figure 3.2 for example. When annotated with some of these labels (rf, po) in Figure 3.3, the nondeterminism disappears and yet the necessary interleavings are never explored, which means that this method discovers equivalence classes among executions without having to generate their elements – this is the advantage of the declarative approach.

As an example for the checks performed by this method, let us see the program in Figure 2.5 again. If we annotate it with the labels  $\{po, rf, ppo\}$  according to *weak* consistency, we get Figure 3.4 – the *ppo* relationship only appears between accesses to the same locations<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>In the case of TSO,  $ppo := po \setminus W * R_{diff} \setminus R * R_{diff}$  and in the case of weak memory,  $ppo := po \setminus W * W_{diff} \setminus W * R_{diff} \setminus R * R_{diff}$ , where  $A * B_{diff}$  means A and B access different variables

Figure 3.3: With this annotation, it is evident that the assertion is violated.

Figure 3.4: Figure 2.5, annotated over a weak memory model

Figure 3.5: Figure 2.5, annotated over a TSO memory model

Take coherence as an example, which in this context can be defined the following way: if a thread has read from another thread's write event, it cannot later read from a **ppo**-previous write event. Because the y := 1 node is not preceded by any other write events in **ppo**, the execution is legal – but if we annotate it as if it was over TSO, we get Figure 3.5, where this property is *violated* and thus we need to discard this execution due to violating coherency.

The main problem with this approach implemented in herd is that it still does not scale well – tests on the scalability of tools handling weak memory done by *Kokologiannakis et al.* [24] indicate that among the other algorithms, *herd* performs the worst because it aims to generate *all* candidate execution graphs and only filters this set to get the *legal* set of executions thereafter.

A promising implementation of a stateless model checking algorithm can be seen in the tool *Nidhugg* [2] – it includes purpose-built algorithms for several well-known architectures (SC, PSO, TSO, POWER), based on a DPOR algorithm for the former three [4], and a combined operational and declarative methodology for POWER [3]. However, as shown by *Kokologiannakis et al.* [24], Nidhugg performs significantly worse than the presented RCMC tool and it cannot handle unique memory models either.

# 3.3 Handling Faults

A novel idea in the field of concurrent model checking is the consideration of using faulty hardware and still being able to verify whether safety criteria are violated when running a program on top of it [10]. This can be useful in a number of ways: for example, having integrated a large amount of microprocessors into a line of products only to later realize that a newly found fault breaks the memory ordering assumptions, it would require a recall without the option to see if a simple software update could solve the issue. This saves not only costs, but the reputation of the company as well, because recalls generally hurt the image of the manufacturer.

To date, there has not been published any solution to this problem other than the theoretical algorithm in the paper I authored [10]. However, there has been work on the *prevention* side of the hardware-software co-verification workflow: the *Check* family of tools [27, 33] aim to ensure that the ISA specification corresponds to the architectural implementation by verifying whether litmus tests with *forbidden* or *allowed* outcomes are indeed *observable* on the architecture – and based on the result, the implementation can be classified as *too strict, too weak* or *correct*. When ran against the RISC-V specification, more than a hundred violations were uncovered that aided the correction of the architecture [33]. However, the utilized approach is not scalable, as these tools use an architectural specification based on the behavior of the hardware to check the programs against – this means that after each instruction, the entire pipeline of the processor has to be simulated. Furthermore, the relations are defined between the different pipeline stages rather than the instructions. This makes it unsuitable for anything other than the small litmus tests they aim to verify.

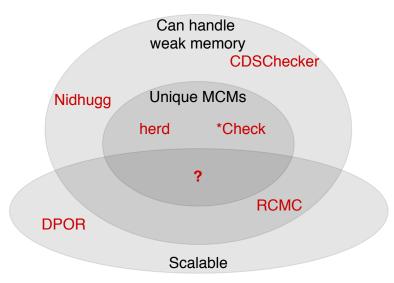

To summarize the introduced approaches, I placed the tools and algorithms claiming to handle concurrent programs on the Venn-diagram in Figure 3.6. Note, that there are no contenders that provide all three aspects: handling weak memory **and** unique memory models, while staying scalable. The proposed algorithm of this work aims to fill this gap and bring concurrent software verification closer to being applicable to any execution environment.

Figure 3.6: Venn-diagram of the related tools and techniques

# Chapter 4

# Algorithm

In this chapter I describe the stateless model checking algorithm that can be parameterized with memory consistency models to provide a tool for verifying weakly ordered architectures. I base the method on the algorithm implemented in *RCMC* [24], but modify it in its roots to be capable of handling the customizable memory models. For the memory models, I use a declarative specification based on a simplified version of the *cat* language [7]. This chapter is structured as follows: in Section 4.1, I show how the algorithm manipulates execution graphs (introduced in Section 3.2.2) to generate all possible execution graphs through informal descriptions and examples. After that, I formalize the algorithm for generating these execution graphs in Section 4.2. Next, I elaborate on the *filtration* possibilities to get the legal executions in Section 4.3 and finally I provide a proof of soundness and optimality in Section 4.4.

The implementation specific parts of this algorithm can be found in Chapter 5.

# 4.1 Execution Graphs

Execution graphs are directed, edge- and vertex-labelled graphs. The vertices' labels contain information on the type of memory instruction they represent:

- W(g, v): Write to g with literal value v.

- $\mathbf{R}(g)$ : Read from g

- F: fence

The edges are labelled with relations akin to the ones defined in Section 3.2.2. Namely:

- po: Relation between immediate successors in the program code

- *rf*: Read-From relation between a Write and a Read that gets its value from the Write

- *mo*: Modification order (total order of Write events to a specific location)

Any other relation (such as ppo) can easily be constructed during filtration, as seen in Section 4.3.

Furthermore, we maintain a set of read nodes called *Revisitables* ( $\mathbb{R}$ ), the importance of which will be explained in further sections.

Figure 4.1: Two threads performing a write and a read operation

(b) New write before initial

It is important to note that an execution graph only contains nodes related to globally accessible variables. Local and thread-local variables are not handled through this algorithm, as they generally behave predictably and deterministically.

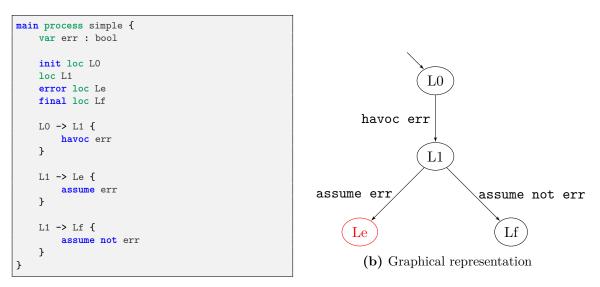

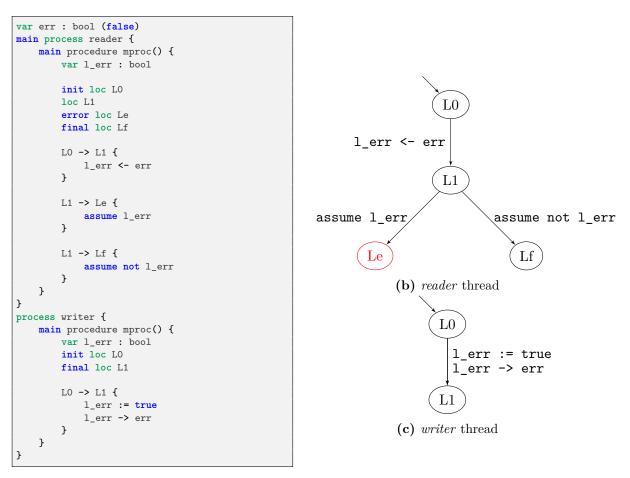

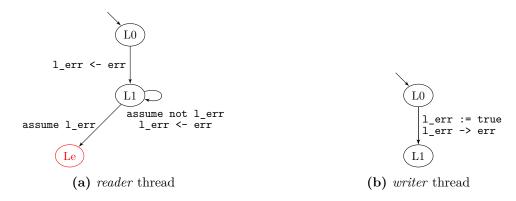

Through the following sections, I show how the execution graphs are generated from the simple program in Figure 4.1.

### 4.1.1 Initial Values

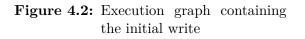

At first, the algorithm starts off with an empty execution graph. As most programming languages (such as C/C++) demand an initial value for all global (or rather, *static*) variables, every such variable will have a corresponding Write node. These are not yet connected to any other vertex, and represent the root(s) of the directed graph later on.

In the example, there is one global variable: x. After creating the corresponding node, the execution graph can be seen in Figure 4.2.

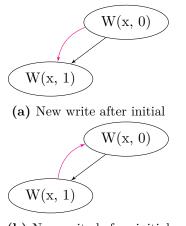

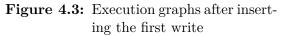

### 4.1.2 Handling a Write

Let us take the Write instruction (W(x, 1)) and see how we need to maintain the three types of relations on the graph. The instruction is sequenced after the initial write, so there must be a **po** edge between them. Furthermore, all possible **mo** sequences have to be explored, so we duplicate the graph and on one we insert the new write *after* the initial write to x, and on the other we insert it *before* that. It seems obvious that only of these executions is sensible – but without knowing the memory model, we have to throw away all presumptions about it, such as that same-address stores are totally ordered in **po**.

At this time there were no Read nodes to accept the written value, so no rf edges were added. The resulting execution graphs can be seen in Figure 4.3.

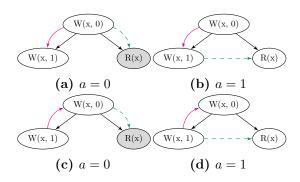

### 4.1.3 Handling a Read

If we take the read instruction now, there are two possible sources it could read from – the initial write W(x, 0), or the other write W(x, 1). We have to explore all possibilities, so

Figure 4.5: Two threads performing two write and two read operations

Figure 4.4: Execution graphs after inserting the read

Figure 4.6: Execution graphs after inserting the read

yet again we duplicate the graphs and draw the corresponding rf edges and the **po** relations between the nodes, in *all execution graphs*. Furthermore, we append the new Read instruction to the set of revisitable reads  $\mathbb{R}$  in every pre-existing execution graph (so in 2 of the resulting 4). The result is visible in Figure 4.4.

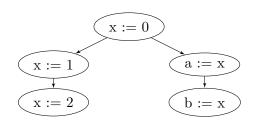

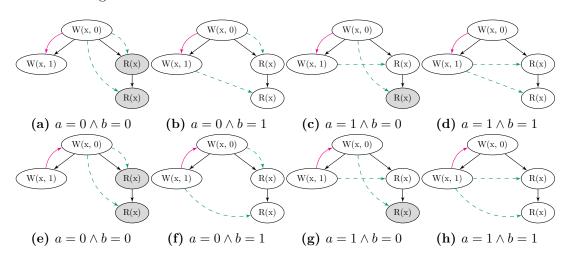

With this addition, the generation of the execution graphs has finished and yielded 4 execution graphs. Now let us extends this example with a new read and new write node, as seen in Figure 4.5!

If we start with the new Read instruction, the process is very similar to the last read – we need to duplicate all existing execution graphs, and in half of them the new read will get its value from the initial value while the other times it reads from W(x, 1). In all preexisting graphs we also mark the new read as revisitable, and place it in the corresponding  $\mathbb{R}$ . However, in every other case we also mark all reads in the new node's  $(po \cup rf)$ -prefix non-revisitable to avoid redundant exploration. The resulting 8 execution graphs can be seen in Figure 4.6.

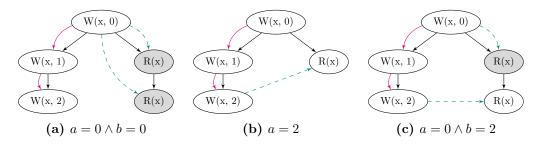

#### 4.1.4 Handling Revisit Sets

If we try to insert the last remaining node W(x, 2), we run into the problem of deciding which (if any) existing reads should get its value instead of the one represented on the

Figure 4.7: One *mo*-order of the subexecutions of Figure 4.6a.

existing graphs. This is where the sets of revisitable reads  $(\mathbb{R})$  come into play: they contain the reads that are not necessarily bound to their current incoming rf edge.

As for **po** and **mo** edges, everything goes as discussed earlier: we bind the first write to the second via a **po** edge, and then multiplicate the graph as many times as necessary to being able to place the new node in **mo** in any order – in this case *before* the **mo**-first write, *after* the **mo**-last write or in-between. This makes the set of execution graphs grow threefold.

After dealing with the **po** and **mo** edges, new **rf** edges have to be added. Firstly, we calculate all *independent* (i.e. the reads cannot reach each other through  $po \cup rf$ ) subsets of  $\mathbb{R}$  to get the so-called *revisit sets*  $\mathcal{R}$ . Afterwards, we yet again multiplicate the graph to get the number of revisit sets, and assign each their own  $\mathcal{R}$ . In each of these execution graphs, the elements of  $\mathcal{R}$  lose their incoming **rf** edges, and instead new **rf** edges are added between the new write and these reads. We remove all  $(po \cup rf)$ -future these reads might have had (as this new value potentially disturbs the program flow later on), and mark these nodes and all of their  $(po \cup rf)$ -predecessors non-revisitable in the resulting  $\mathbb{R}$ .

Following this procedure, we are left with 42 execution graphs<sup>1</sup>. This is more than I can present here, so I included only a subset of the subexecutions of Figure 4.6a in Figure 4.7. Note the lack of an  $a = 2 \wedge b = 2$  outcome – because we revisited the first read, its entire future had to be erased as to not breach program flow. However, that outcome *will* be generated – the missing read can be re-added with all the rules that apply when handling a read, and there will be a corresponding outcome.

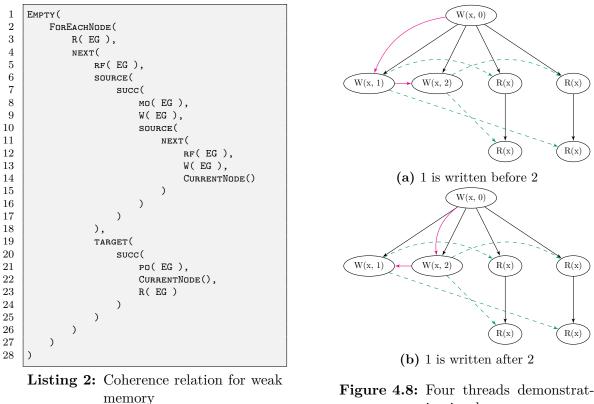

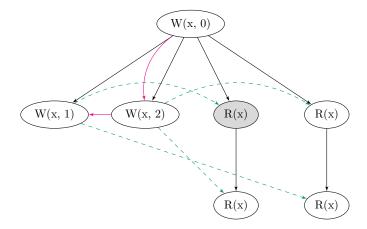

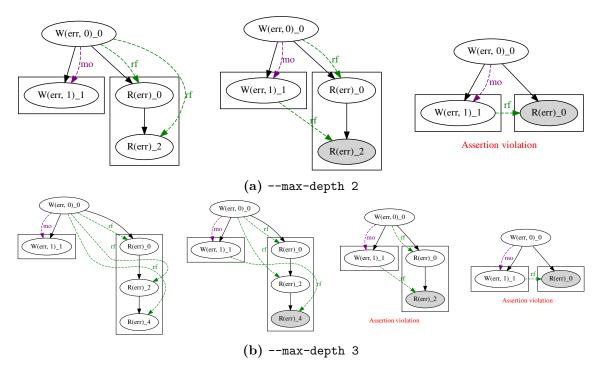

#### 4.1.5 Effect of the Memory Model

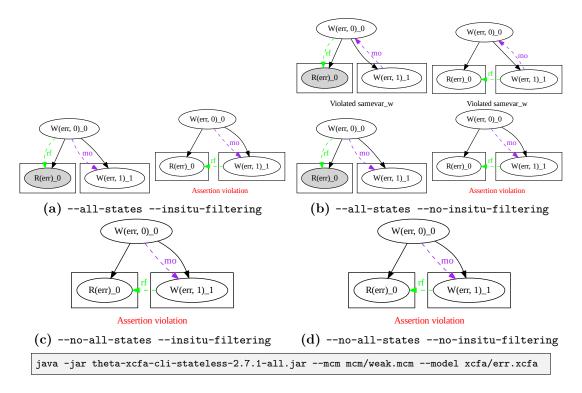

As we have previously seen, even a seemingly simple program might have numerous execution graphs due to the different combinations of rf-edges and mo-orders. However, most of these combinations are most likely illegal according to the underlying memory model – the execution graphs greatly outnumber *consistent* execution graphs in most cases. However, striving to be memory consistency-independent, the algorithm cannot discard executions without proof that a specific execution will cause a memory model violation.

In this work, I evaluate two separate approaches to this problem. One method is to generate all execution graphs without paying attention to legality, until such an execution is found that violates the safety criteria. If that execution is allowed by the memory model, the violation is observable and should be reported that the program does not

<sup>&</sup>lt;sup>1</sup>Revisiting 4.6a and 4.6e yield 3-3 new execution graphs, 4.6c and 4.6g yield 2-2 and the others remain untouched. Growth from the *mo* order is threefold, so 3 \* (3 + 1 + 2 + 1) \* 2 = 42 new graphs are created.

```

Algorithm 1: EXECUTIONGRAPHS(p) returns the set of execution graphs in p

Input: A program p(T, Q)

Output: The set of execution graphs in p

1 \mathbb{S} \leftarrow \{(INITIALSTACK(T), EMPTYGRAPH(), T)\}

2 \mathbb{E}\mathbb{G} \leftarrow \emptyset

3 while |\mathbb{S}| > 0 do

(S, EG, E) \leftarrow s \in \mathbb{S}

4

\mathbb{S} \leftarrow \mathbb{S} \setminus \{(S, EG, E)\}

5

while \negIsBlocked(p, S, E) do

// IsBLOCKED returns true if p is blocked

6

q \leftarrow \text{GETNEXTSTMT}(p, S, E) // GETNEXTSTMT returns an enabled statement

7

\mathbb{S} \leftarrow \mathbb{S} \cup \text{EXECUTE}(q, s)

8

// EXECUTE builds EG, returns new states

end

9

\mathbb{EG} \leftarrow \mathbb{EG} \cup \{EG\}

10

11 end

12 return EG

```

satisfy its requirements. Otherwise, the search continues until such a violation is found, or all executions are explored.

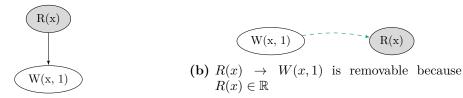

Another method is to keep track of violations as they happen. A disadvantage of this approach is the overhead of checking for violations every time a new element is added to the execution graph, but this can potentially generate significantly fewer executions in comparison with the former approach. The key idea is to classify violations as *transient* or *permanent* based on the possibility of being dissolved by the rules of execution graph construction. If a *permanent* violation is found, no subexecution of the execution graph can be legal (as the violation can never be dissolved), and therefore there is no need in exploring them. If however, a *transient* violation is found, it does not permit this broad discarding procedure but rather potentially filters the threads that can supply new instructions. The details to this approach can be found in Section 4.3.

# 4.2 Generating the Executions

In this section I formalize the algorithm introduced in Section 4.1. To summarize its goals:

- The algorithm should generate all possible execution graphs of its input program

- No execution graph should be generated multiple times

- All subexecutions are *self-contained*, i.e. they are entirely independent of each other (to achieve statelessness)

The entry point to this algorithm is the **EXECUTIONGRAPHS** procedure, visible as Algorithm 1. At first, the set of current states S is initialized with the starting state of the program, expressed as a tuple (S, EG, E). This tuple is slightly different from the one defined in Definition 2.1.2, as the global valuation has been replaced with an execution graph EG. However, EG contains a superset of the information contained in the global valuation (as this is readily available in the form of rf edges), so we do not lose any information.

The main loop of the algorithm (starting at line 3) runs until there are no more states to be explored in S and fills up the previously initialized set EG with execution graphs, by

choosing one in each iteration (s) the elements of which are S, EG, E, respectively. Firstly, this element is subtracted from  $\mathbb{E}\mathbb{G}$  (to avoid being used multiple times), then all of its instructions are processed in the loop starting in line **6**. This loop runs until all threads become blocked (i.e. they have finished execution, or are blocked by some other construct – indicated by the predicate ISBLOCKED), as after that no instructions remain to be processed. If execution has not yet finished, let q be an *enabled* statement (i.e. in a non-blocked thread, fulfilling all possible prerequisites in S) received from GETNEXTSTMT. After processing q in EXECUTE (see Section 4.2.1), we add the newly created states to S. If a *blocked* state is reached, we add the execution graph EG to the  $\mathbb{E}\mathbb{G}$  set. When the set of states S is empty, we return  $\mathbb{E}\mathbb{G}$  and the algorithm is finished.

#### 4.2.1 Executing a Statement

For the purposes of this algorithm, there are four distinct types of statements in a program:

- 1. Read instructions (assigning a local variable the value of a global variable)

- 2. Write instructions (assigning a literal to a global variable)

- 3. Fence instructions (semantics depends on the memory model)

- 4. Other instructions (local variable assignments, program flow modifiers, etc.)

The  $4^{th}$  type of statement is only used by the algorithm to determine which statements are enabled (in the form of an *if* or *assume* statement, for example) and to keep track of the local variables which appear on the local valuation. These statements are *not* present on the execution graphs, unlike the first three, which appear directly.

The first three types are handled by the procedures NEWREAD, NEWWRITE and NEWFENCE, respectively, which are called by the EXECUTE procedure based on their type. The role of these procedures is to maintain the set of revisitable reads  $\mathbb{R}$ , and insert or delete nodes and edges in the execution graph EG. The NEWFENCE procedure only places the fence at the end of the corresponding thread with a **po** edge, and therefore it will not be further discussed. Its importance will come up in Section 4.3.

Note, that for the sake of simplicity the  $\mathbb{R}$  set is assumed to contain reads from a single memory location. Were this not the case, a simple filtration can yield the variable-specific set of revisitable reads, after which it behaves exactly as described.

#### 4.2.1.1 NEWREAD

When processing a read statement  $q_r$ , the goal is to find suitable write statements to read from, and to make sure any future write statement will be able to supply a value as well. To make this happen, we must explore all such subexecutions of EG where  $q_r$  reads from an existing write, and in exactly one of those subexecutions we also add  $q_r$  to the set of revisitable reads  $\mathbb{R}$ . This means that in exactly one subexecution the write  $q_r$  reads from is not fixed, and therefore any future write might *revisit* it, i.e. supply its own value to  $q_r$ .

The algorithm that satisfies these requirements can be seen as Algorithm 2. It iterates over all the writes to the global variable where  $q_r$  reads from, and it creates a new state with an added  $w \in W \to q_r \ rf \ edge^2$  for every such w. In all but the last case (where the

<sup>&</sup>lt;sup>2</sup>And the po edges as well (from the last instruction of the given thread when that exists, or all the initial writes if it does not)

Algorithm 2: NEWREAD $(q_r, s)$  returns the set of new states after adding  $q_r$

**Input:** A read  $q_r(l, q)$  and a state s(S, EG, E) (*l*: local-, *g*: global variable) **Output:** The new states after applying  $q_r$  to s  $1 \ \mathbb{S} \leftarrow \emptyset$ **2**  $W \leftarrow W(EG, g)$ // All writes in EG writing to g**3 while** |W| > 0 **do**  $w \in W$  $\mathbf{4}$  $W \leftarrow W \setminus \{w\}$ 5 if |W| = 0 then 6  $s \leftarrow \text{ADDRREAD}(s, w, q_r)$  // ADDRREAD creates a revisitable read  $w \rightarrow q_r$ 7 8 else  $s' \leftarrow \text{ADDREAD}(s, w, q_r)$ // ADDREAD creates a simple read  $w

ightarrow q_r$ 9  $\mathbb{S} \leftarrow \mathbb{S} \cup \{ \text{MarkFinal}(s', \{w, q_r\}) \}$ 10 // MARKFINAL marks the (po  $\cup$  rf)-predecessors non-revisitable end 11 12 end 13 return S

remaining W set is empty), this new state gets put into S, where it corresponds to a newly created and to-be-explored subexecution. When the last w is processed, the resulting state replaces the old state of the execution under construction.

An important difference between the new states and the current state's replacement is *revisitability*. When the current state is replaced with a new one,  $q_r$  is marked to be *revisitable*, and is put into  $\mathbb{R}$ . In all other cases, the read is not only not marked to be *revisitable*, but all  $(\mathbf{po} \cup \mathbf{rf})$ -predecessors of both w and  $q_r$  are marked as non-revisitable as well. This is done to avoid redundant exploration – the set of revisitable reads that we discarded this way are included as a subset of the  $\mathbb{R}$  set in the former case, and are therefore properly handled.

#### 4.2.1.2 NEWWRITE

A write statement  $q_w$  is the source of rf edges and supply the values to read statements. When a new one is added, on the one hand all possible rf edges need to be drawn, while on the other all possible *mo*-orders have to be generated, while remaining nonredundant in all subexecutions (and therefore optimal in the terms of generated execution graphs). Special care has to be taken when generating the *mo*-orders, because those are not reflected in the final execution graphs as value assignments, and therefore it is easy to create non-unique subexplorations.

The resulting algorithm can be seen as Algorithm 3. It starts off by creating two sets:

- R: The set of all possible revisit sets  $\mathcal{R}$ . This includes all subsets of  $\mathbb{R}$  filtered by the INDEPENDENT function, which only lets sets containing  $(po \cup rf)$ -independent reads remain.

- W: The set of (ordered) list of writes to the same memory location as  $q_w$ , with the new write  $q_w$  included at every possible position.

Algorithm 3: NEWWRITE $(q_w, s)$  returns the set of new states after adding  $q_w$

**Input:** A write  $q_w(g, v)$  and a state s(S, EG, E) (g: global variable, v: value) **Output:** The new states after applying  $q_w$  to s  $1 \ \mathbb{S} \leftarrow \emptyset$ **2**  $R \leftarrow \text{INDEPENDENT}(2^{\mathbb{R}(EG)})$ // Set of all possible independent  $\mathcal{R}s$ **3**  $W \leftarrow \text{SEQUENCE}(W(EG, g))$ // All sequences among writes in EG writing to qwhile |R| > 0 do 4  $\mathcal{R} \in R, R \leftarrow R \setminus \{\mathcal{R}\}$  $\mathbf{5}$ 6 while |W| > 0 do  $w \in W, W \leftarrow W \setminus \{w\}$ 7  $s' \leftarrow \text{UPDATEMO}(s, w)$ // UPDATEMO updates the mo-order to reflect w8 while  $|\mathcal{R}| > 0$  do 9  $r \in \mathcal{R}, \mathcal{R} \leftarrow \mathcal{R} \setminus \{r\}$ 10  $s' \leftarrow \text{INVALIDATE}(s', r)$ // INVALIDATE invalidates r's (po  $\cup$  rf)-future 11  $s' \leftarrow \text{ADDREAD}(s', q_w, r)$ 12 $s' \leftarrow \text{MarkFinal}(s', \{r\})$  $\mathbf{13}$ end 14 if  $|W| > 0 \land \neg is\_last_w(q_w)$  then  $s' \leftarrow MARKFINAL(s', \{succ_w(q_w)\})$  $\mathbf{15}$ if  $|W| = 0 \land |R| = 0$  then 16  $s \leftarrow s'$  $\mathbf{17}$ else18  $\mathbb{S} \leftarrow \mathbb{S} \cup \{ \text{MarkFinal}(s', \{q_w\}) \}$ 19  $\mathbf{20}$ end  $\mathbf{21}$ end 22 end 23 return S

The procedure then iterates over the elements of the product of these two sets, and in each step it updates the *mo*-order to that of  $w \in W$ , and then performs the following actions on  $\mathcal{R} \in R$ :

- 1. Invalidates the effects of  $\forall r \in \mathcal{R}$  on the execution graph (i.e. removes all nodes from their  $(po \cup rf)$ -future)

- 2. Adds a (non-revisitable) rf edge between  $q_w$  and every  $r \in \mathcal{R}$

- 3. Removes  $\forall r \in \mathcal{R}$  and all of their  $(po \cup rf)$ -predecessors from  $\mathbb{R}$

If this iteration is not yet final over W, and  $q_w$  is not the last element of the **mo**-order, all reads  $(\mathbf{po} \cup \mathbf{rf})$ -preceding the **mo**-next write of  $q_w$  in w are removed from the revisit set  $\mathbb{R}$ .

Afterwards, the procedure adds this newly created state (while marking all  $(po \cup rf)$ predecessors of  $q_w$  non-revisitable) to the set of new states (S) – unless it is the last

iteration over  $W \times R$ , in which case the old state is replaced by this new state in the

subexecution that called NewWRITE in the first place. With this step, the procedure

concludes and returns S.

So far, the algorithm generates all possible execution graphs, without paying attention to legality. As discussed earlier, this is one of the approaches to this problem – generate all executions first, and when a safety violation is found, check if the execution leading up

to it was legal. However, there is also the approach when we want to eliminate illegal instructions early on. In this case, the procedures adding to and removing from the execution graphs (nodes and/or edges) must test the result for violations, and either stop the subexecution's exploration (in the case of a permanent violation), or constrain the enabled threads (when a transient violation is found).

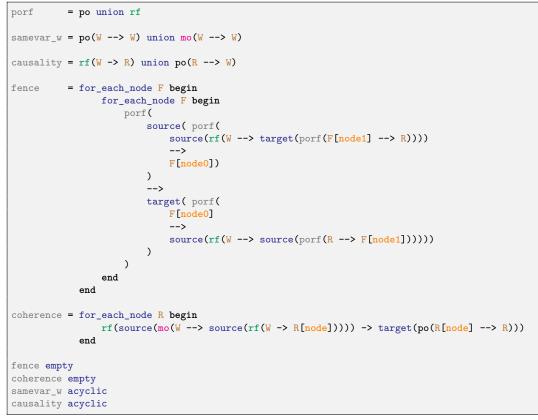

### 4.3 Is an Execution Legal?

Inspired by the *cat* language [7] employed by *herd* [6], memory inconsistency patterns are described over an execution graph using:

- 1. its edges and nodes,

- 2. constructs of these edges and nodes, and

- 3. their primitive properties such as *acyclicity*, *emptyness* and *irreflexivity*.

The edges that the execution graph contains by default (as seen in previous sections) are po, mo and rf edges. Nodes are Writes, Reads and Fences. Expressions (constructs) among these edges can be of the following types (expressed as n-ary functions):

- 1. EMPTY()  $\rightarrow$  new empty execution graph

- 2. NEXT $(EG, EG_1, EG_2) \rightarrow$  new execution graph only containing existing edges in EG, whose origin nodes are in EG<sub>1</sub> and target nodes are in EG<sub>2</sub>

- 3.  $SUCC(EG, EG_1, EG_2) \rightarrow$  new execution graph only containing edges between nodes that reach each other in EG, whose origin nodes are in EG<sub>1</sub> and target nodes are in EG<sub>2</sub>

- 4. SOURCE $(EG) \rightarrow$  new execution graph only containing edges' origin nodes in EG

- 5. TARGET $(EG) \rightarrow$  new execution graph only containing edges' target nodes in EG

- 6. MULTIPLY $(EG_1, EG_2) \rightarrow$  new execution graph containing edges between all nodes of EG<sub>1</sub> and EG<sub>2</sub>

- 7. SUBTRACT $(EG_1, EG_2) \rightarrow$  new execution graph containing the differences between EG<sub>1</sub> and EG<sub>2</sub>

- 8. INTERSECT $(EG_1, EG_2) \rightarrow$  new execution graph containing the intersection of EG<sub>1</sub> and EG<sub>2</sub>

- 9. UNION $(EG_1, EG_2) \rightarrow$  new execution graph containing the union of EG<sub>1</sub> and EG<sub>2</sub>

Furthermore, execution graphs can be *filtered* by type (edge- and node types as well), and we also define expressions for the following constructs:

- 1. FOREACHTHREAD $(expr) \rightarrow expr$  is evaluated for  $\forall t \in T$

- 2. FOREACHVARIABLE $(expr) \rightarrow expr$  is evaluated for  $\forall v \in Q$

- 3. FOREACHNODE $(EG, expr) \rightarrow expr$  is evaluated for  $\forall node \in EG$

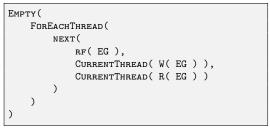

Listing 1: Constraint on the lack of intra-thread *rf* edges

For each of these complex constructs, nodes can be filtered by the current iteration of threads, variables or nodes – for example, in Listing 1, the CURRENTTHREAD filter will only let those nodes in EG pass through to the NEXT function, which are in the thread of the current iteration step in FOREACHTHREAD.<sup>3</sup>

Furthermore, properties (*acyclicity*, *irreflexivity* and *emptyness*) can be combined through the Boolean operations *and* and *or*, but cannot be negated (see Section 4.3.1 for justification).

Beside following rules constructed from the expressions above, memory models must also abide by the following rules:

- Reads can only read from existing writes<sup>4</sup>

- Both Writes and Reads behave *correctly*, i.e. they atomically interact with exactly one memory location (and that location is fixed from the source)

However, if these constraints are satisfied, any memory model can be specified. To justify this, consider the constructs the *cat* language describes [7]. It is easy to see that all such constructs either exist in this model as well, or can be created by combining some functions above – see Appendix A.

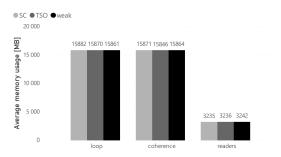

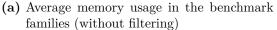

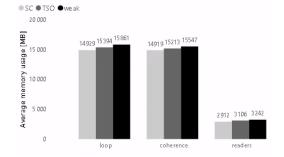

### 4.3.1 Permanence